микропроцессорная техника

УДК 681.3-181.4

А. В. Бокарев, М. Ю* Гамории» А. И. Кабанов

бис адаптера магистралей см эвм и микроэвм

«электроника 60»

Для сопряжения магистрали микро-

эвм «Электроника МС 1201.01»

(«Электроника 60»), удовлетворяю-

щей требованиям интерфейса МПИ

[1, 2] с устройствами ряда СМ ЭВМ

(«Электроника 100/25», «Электрони-

ка 79»), имеющими интерфейс «Об-

щая шина» [3J, разработаны устрой-

ства сопряжения [4, 5], выполнен-

ные на микросхемах малой и средней

интеграции» Для уменьшения габа-

ритов и потребляемой мощности та-

ких устройств предлагается BHG со-

пряжения К1801ВП1-054, выполнен-

ная в 42-выводном корпусе по N-

МОП технологии. БИС формирует

временные последовательности сигна-

лов интерфейсов МПИ и ОШ при

выполнении операций запись, чте-

ние, ч т е н и е-м о д и ф и к а ц и я-з а-

пись, захват магистрали, пе-

редача вектора прерывания.

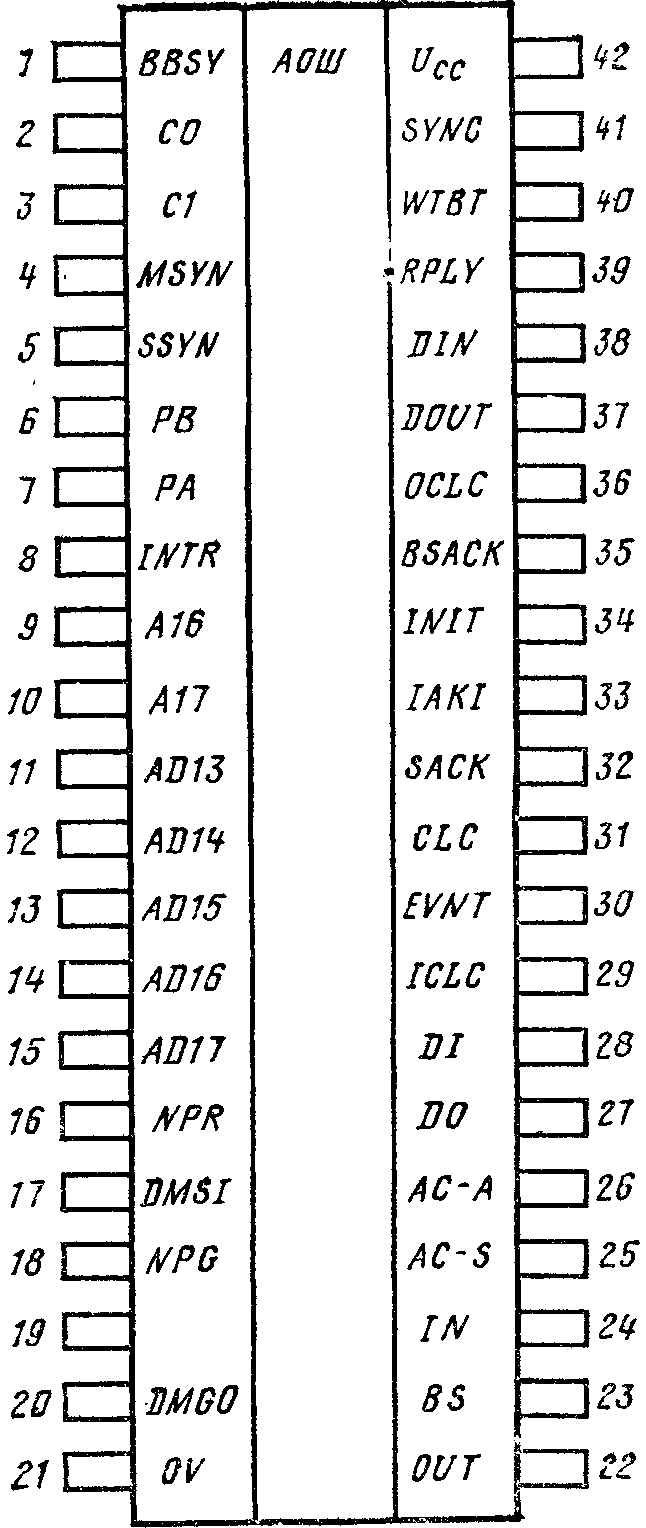

Условное графическое обозначение

БИС приведено на рис* 1, Функцио-

нальное назначение сигналов показа-

но в таблице.

Микросхема включает в себя сле-

дующие блоки:

блок управления передачей инфор-

мации (передачей адресов) между

магистралями при выполнении опера-

ций обмена; при этом устройство,

инициирующее передачу информа-

ции, может находиться как на маги-

страли МПИ, так и на магистрали

ОШ;

с) по порядку расположения выводов;

6) по функциональному назначению вы*

цодоз

Рис, 1. Условное графическое обозна-

чение БИС К1801ВП1-054;

с) по порядку расположения выводов;

6) по функциональному назначению вы*

цодоз

блок формирования сигналов МГШ

и ОШ при обмене данными между

магистралями осуществляет управле-

ние передачей вектора прерывания из

магистрали ОШ в МПИ и трансля-

цию разрешения прямого доступа из

магистрали МПИ в ОШ;

блок синхронизации;

генератор тактовых импульсов,

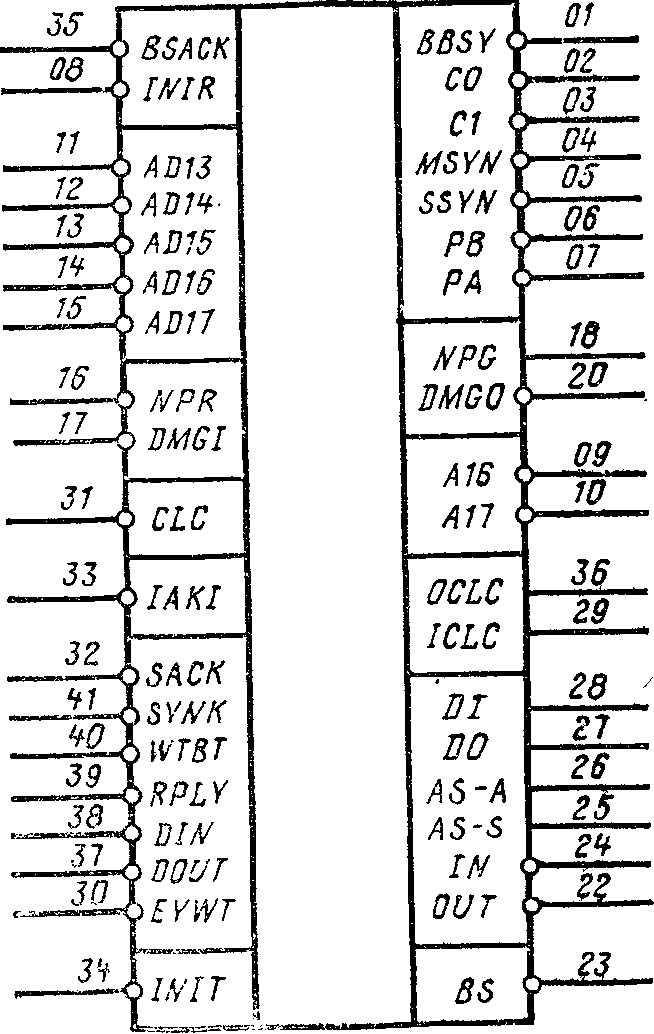

Работа БИС в режимах чтение и

запись с магистрали МПИ. В начале

каждого адресного обмена ус-

тановкой низкого уровня сигнала

SVNC магистрали МПИ формируют-

ся два старших разряда адреса иа

выводах А16, А17 и низкий уровень

сигналов OUT, BBSY магистрали ОШ,

а также сигнал передачи адреса

AC-S на магистраль ОШ.

Чтение в магистраль МПИ,

Признаком чтения данных является

низкий уровень сигнала DIN на вхо-

де БИС магистрали МПИ. Появление

сигнала разрешает формирование

высокого уровня сигналов приема

данных D1, кода управления СО, С!

и разрешения запуска схем блока

синхронизации с генератором такто-

вых импульсов для формирования

временной задержки (150 не) MIN

сигнала MSYN относительно кода

управления (СО, С1). Чтение продол-

жается до появления на выводе

RPLY низкого уровня в магистрали

МПИ в ответ на сигнал SSYN низко-

го уровня магистрали ОШ. Прием

данных заканчивается установлением

высокого уровня на выводе D1N, за-

тем снятием сигналов MSYN, DL

Временная диаграмма работы БИС

в режиме чтения в магистраль МПИ

приведена на рис. 2,а.

Запись из магистрали

МПИ. Признаком установки данных

является низкий уровень на выводе

DOUT магистрали МПИ. Сигнал

DOUT формирует высокий уровень

на выводе DO сигнала передачи дан-

ных на магистраль ОШ, а также низ-

кий уровень С1 кода управления и

высокий уровень СО, если на момент

прихода сигнала DOUT на выводе

WTBT установлен высокий уровень,

Одновременно сигналом DOUT за-

пускается блок синхронизации для

формирования временной задержки

(150 не) сигнала MSYN. Операция

записи продолжается до появления

на выводе RPLY низкого уровня в

|

Вывод |

Обозначение |

Назначение |

Характери-

стика вывода |

Уровень ак-

тивного

напряжения |

|

1

2, 3 |

BBSY

СО, С1 |

Сигнал занятости ма-

гистрали ОШ

Разряды кода опера-

ции обмена на маги-

страли ОШ |

Вход-вы-

ход

То же |

Низкий

То же |

|

|

|

С1 |

со | Операция |

|

|

|

|

MSYN

SSYN

РВ, РА

INTR

А16, А17

AD13...AD17

NPR

DMGI

NPG |

0

0

1

1 |

0 Чтение слова

1 Чтение слова

с паузой

0 Запись слова

1 Запись байта |

|

|

|

4

5

6, 7

8

9, 10

11...15

15

17

18 |

Сигнал синхрониза-

ции задатчика на ма-

гистрали ОШ

Сигнал синхрониза-

ции исполнителя на

магистрали ОШ

Разряды кода приз-

нака ошибки при пе-

редаче данных по ма-

гистрали ОШ

Сигнал разрешения

прерывания

Разряды адреса ма-

гистрали ОШ

Разряды адреса-дан-

ных магистрали МПИ

используются для

формирования сигна-

ла ВУ

Запрос прямого дос-

тупа от устройств

магистрали ОШ

Разрешение захвата

магистрали МПИ

(приемник)

Разрешение прямого

доступа магистрали

Разрешение захвата

магистрали МПИ (ис-

точник)

Корпус

Управление приемо-

передатчиками интер-

фейсных сигналов ма-

гистрали ОШ

Выбор внешних уст-

ройств на МПИ

Управление приемо-

передатчиками ин-

терфейсных сигналов

магистрали МПИ

Признак передачи ад-

реса в магистраль ОШ

Признак приема ад-

реса из магистрали |

То же

То же

То же

То же

Выход

Вход

То же

То же

Выход |

То же

То же

То же

То же

То же

То же

То же

Высокий |

|

20

21

22

23

24

25

26 |

DM СО

GND

OUT

BS

IN

AC-S

AS-A |

То же

То же

То же

То же

То же

То же |

Низкий

То же

То же

То же

Высокий

То же |

|

27 |

DO |

ОШ

Признак передачи

данных в магистраль

ОШ

Признак приема дан-

ных из магистрали

ОШ

Пуск тактового гене-

ратора |

То же |

То же |

|

28 |

DI |

То же |

То же |

|

29 |

ICLC |

То же |

То же |

ответ на сигнал SSYN. Запись дан-

ных заканчивается установлением на

выводе DOUT высокого уровня. Сня-

тие сигнала DOUT устанавливает

высокий уровень на выводе MSYN.

Временная диаграмма работы БИС в

режиме записи из магистрали МПИ

приведена на рис. 2,6.

Для всех видов адресного обмена

чтения-записи слова окончание теку-

щего цикла обмена и переход к сле-

дующему циклу выполняются одина-

ково.

При получении сигнала RPLY уст-

ройство — инициатор обмена на ма-

гистрали МПИ заканчивает обмен,

устанавливая высокий уровень на

выводе SYNC. БИС в ответ на сня-

тие сигнала SYNC устанавливает вы-

сокий уровень на выводах BBSY,

OUT.

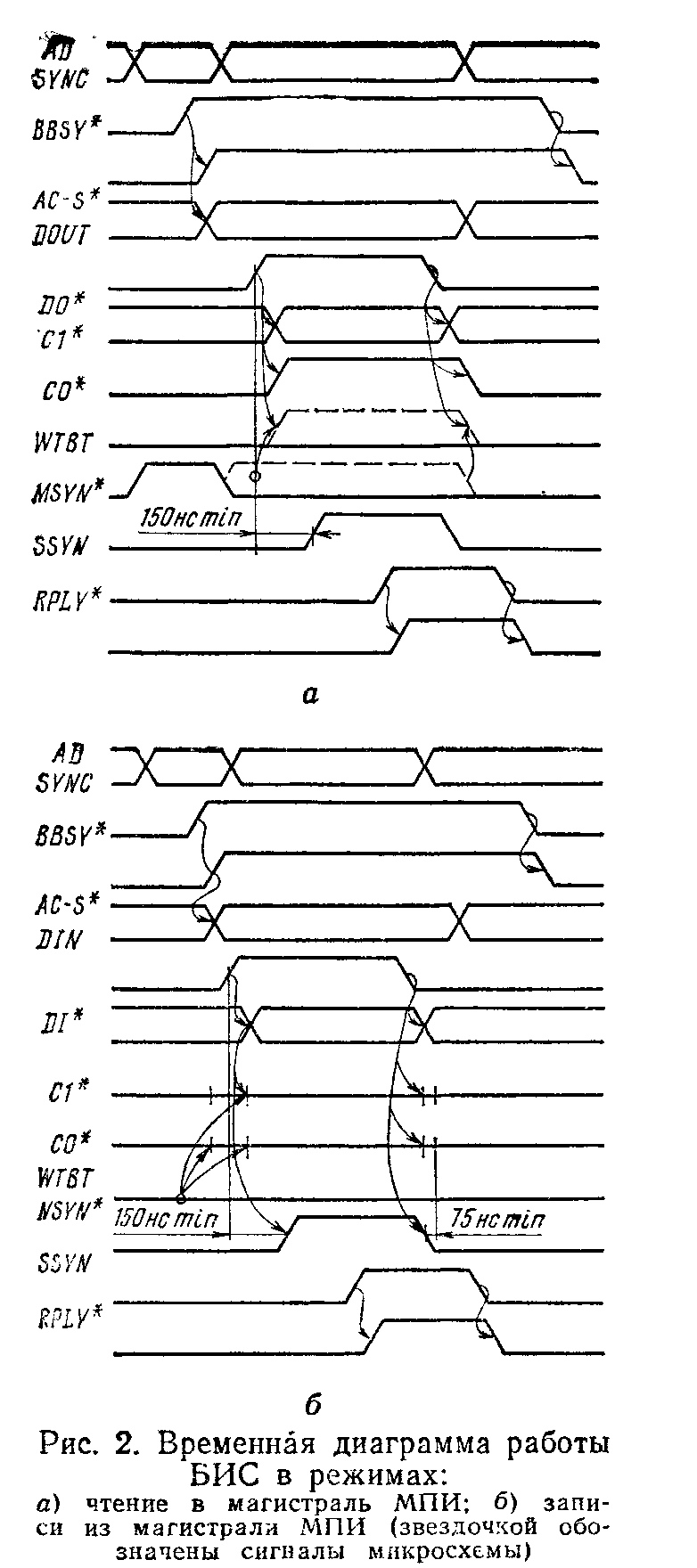

Работа БИС в режимах чтение и

запись с магистрали ОШ. (Устройст-

во — инициатор обмена в магистра-

ли ОШ начинает обмен только после

операции захвата магистрали МПИ.)

Продолжение табмщы SBSY

|

вы рол |

Обозначение |

Назначение |

Характер?!- -

пика вывода |

Уровень ак-

тивного

напряжете |

|

30 |

EVNT |

Ошибка при переда- |

Вход-вы- |

Низкий |

|

|

|

че данных по магисг |

ход |

|

|

|

|

рали МПИ |

|

|

|

31 |

CLC |

Тактовая частота |

Вход |

То же |

|

32 |

SACK |

Подтверждение за- |

Вход-вы- |

То же |

|

|

|

проса при захвате |

ход |

|

|

|

|

магистрали М.ПИ |

Вход |

|

|

33 |

IAKI |

Разрешение преры- |

То же |

|

|

|

вания в магистраль |

|

|

|

|

|

ОШ |

|

|

|

31 |

i'NIT |

Сброс магистрали |

То же |

То же |

|

|

|

МПИ |

|

|

|

35 |

BSACK |

Подтверждение вы- |

То же |

То же |

|

|

|

борки при захвате |

|

|

|

|

OCLC |

магистрали ОШ |

|

|

|

36 |

Тактовая частота |

Выход |

То же |

|

37 |

DOUT |

Запись данных на |

Вход-вы- |

То же |

|

|

|

магистрали МПИ |

ход |

|

|

38 |

DIN |

Чтение данных на ма- |

То же |

То же |

|

|

|

гистрали МПИ |

|

|

|

39 |

RPLY |

Ответ устройств ма- |

То же |

То же |

|

|

|

гистрали МПИ |

|

|

|

40 |

WTBT |

Признак записи на |

То же |

То же |

|

|

|

магистрали МПИ |

|

|

|

41 |

SYNC |

Признак обмена на |

То же |

То же |

|

42 |

|

магистрали МПИ |

|

|

|

Ucc |

Питание 5 В |

|

|

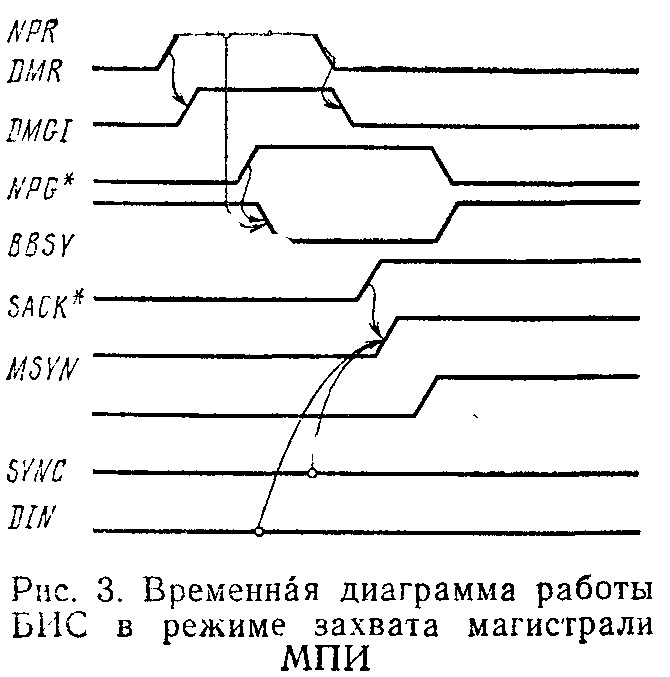

Захват магистрали. Появ-

ление на выводе NPG высокого уров-

ня сшнала разрешения прямого до-

ступа магистрали ОШ осуществляет-

ся при наличии низкого уровня на

выводе NPR сигнала прямого досту-

па магистрали ОШ и низкого уровня

на выводе DMGI сигнала разреше-

ния прямого доступа МПИ.

Формируется низкий уровень сиг-

нала SACK в ответ на сигналы BBSY,

BSACK низкого уровня при наличии

высоких уровней на выводах SYNC,

DIN, RPLY и сигнал низкого уровня

на выходе IN.

Временная диаграмма работы БИС

в режиме захвата магистрали МПИ

приведена на рис. 3.

Устройа во, инициирующее обмен,

после установки BBSY устанавлива-

ет на выводах СО, С1 код управле-

ния. С приходом сигнала низкого

уровня MSYN внутренней логикой де-

шифрируется код управления. Одно-

временно устанавливается высокий

уровень сигнала передачи адреса

АС-А на магистраль МПИ.

Если сигналы СО, С1 имеют высо-

кий уровень (чтение в магистраль

ОШ), то БИС формирует сигнал

WTBT и через 250 не MIN в ответ

на сигнал MSYN-сигнал DIN. Вре-

менная диаграмма работы БИС в ре-

жиме чтения в магистраль ОШ при-

ведена на рис. 4,а.

Если СО — высокий уровень, a С1—

низкий уровень (запись из магист-

рали ОШ), то формируется сигнал

WTBT низкого уровня на время пе-

редачи адреса, а через 350 не MIN-

сигнал DOUT в ответ на сигнал

MSYN. Временная диаграмма работы

БИС в режиме записи из магистра-

ли ОШ приведена на рис. 4,6.

С приходом сигнала MSYN БИС

формирует низкий уровень на выво-

де SYNC с временной задержкой

150 не MIN. С поступлением низкого

уровня сигнала RPLY БИС форми-

рует временную задержку сигнала

SSYN в среднем на 200—250 не MIN

в зависимости от кода управления.

Временная задержка сигналов SYNC,

DIN, DOUT, SSYN формируется с

дискретностью частоты управляюще-

го генератора.

Снятие сигнала MSYN приводит к

снятию сигналов DIN или DOUT. Ко-

нец процесса обмена со стороны ма-

гистрали ОШ характеризуется уста-

новлением высокого уровня на выво-

де BBSY. При снятии сигнала BBSY

устанавливается высокий уровень на

выводах SACK, SYNC, IN.

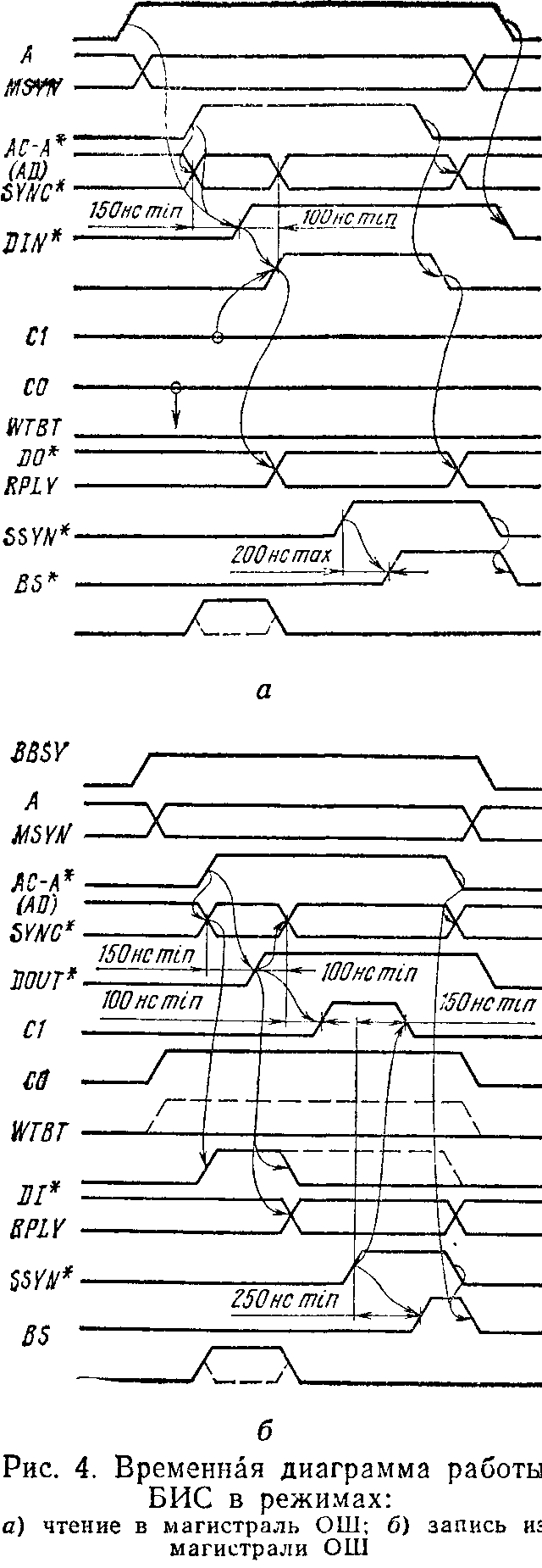

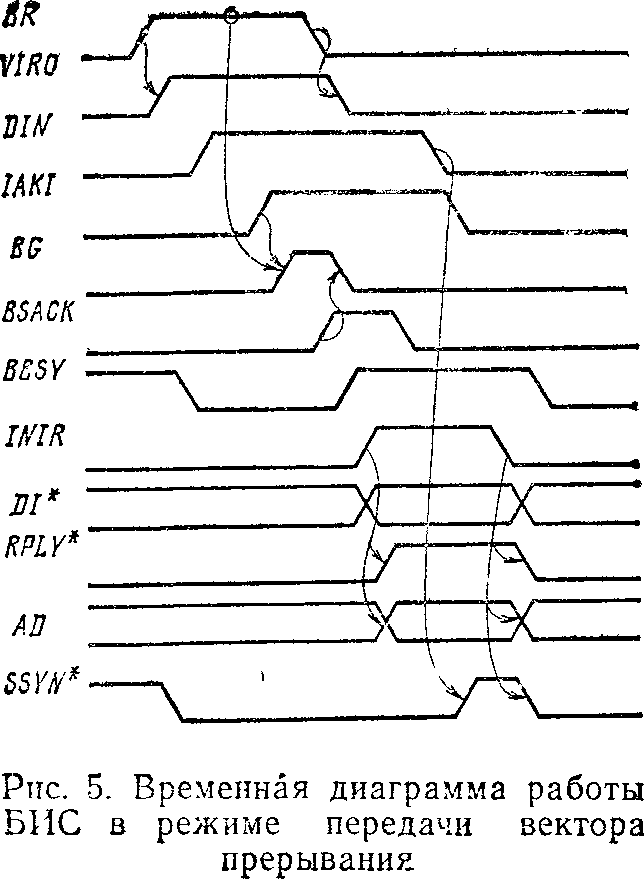

Передача вектора преры-

вания. Разрешением на прием век-

тора прерывания процессором явля-

ется установка сигналов низкого

уровня на выводах DIN, IAKI (сиг-

нала разрешения прерывания). В от-

вет на сигнал 1AKI с магистрали ОШ

поступают сигналы низкого уровня

BBSY, INTR. С приходом INTR БИС

устанавливает сигналы RPLY низкого

уровня и сигнал DI. Процессор сни-

мает сигнал DIN, IAKI. БИС в ответ

на установку высокого уровня на вы-

водах DIN и IAKI устанавливает

низкий уровень сигнала SSYN. Уст-

ройство — инициатор передачи век-

тора прерывания снимает сигнал

INTR. В ответ БИС устанавливает

высокие уровни на выводах RPLY,

SSYN. Высокий уровень сигнала

SSYN сбрасывает сигнал BBSY в ма-

гистрали ОШ. Временная диаграмма

работы BHG в режиме Передачи век-

тора прерывания Приведена на рис.

5. Сигнал 1NIT используется в на-

чальной установке системы или для

установки исходного состояния в про-

цессе ее работы.

Телефон для справок: 532-84-22,

Москва.

ЛИТЕРАТУРА

1. ОСТ 11 305.903—80. Микропроцес-

сорные средства вычислительной

техники. Технические средства. Ин-

терфейс межмодульный. Техниче-

ское описание.

2. ГОСТ 26765.51—86. Интерфейс

магистральный параллельный МПИ

системы электронных модулей.

Общие требования к совокупности

правил обмена информацией,

3. ОСТ 25 795—78. Система малых

электронных вычислительных ма-

шин. Интерфейс «Общая шина».

4. Лопатин В» С.* Ю р о ч к и н

A. Г., Баран о в Н. Д. Адаптер

магистралей СМ ЭВМ и микро-

ЭВМ «Электроника 60» // Микро-

процессорные средства и систе-

мы.— 1985.— № 1.— С. 11—12.

5. Системные средства сопряже-

ния для микроЭВМ / В. С. Бори-

сов, EL П. К у л и к о в, А. А. О в-

д и е н к о и др. // Электронная про-

мышленность. — 1983. — № 9. — С.

59—62.

6. Микропроцессорные комп-

лекты интегральных схем. Состав и

структура / В. С. Борисов, А. А.

Васенков, Б. М. Малашев и ч

и др. // Под ред. А. А. Васенкова и

B. А. Шахнова.—М.: Радио и

связь, 1982.— 192 с.

Статья поступила 29 января 1987 г.

УДК 681.3—281.4

А. В. Бокарев, IYI. Ю. Гаморин, А. И. Кабанов

адаптер магистралей

мпи —ош

Предназначен для аппаратного преобразования сиг-

налов межмодульного параллельного интерфейса (МГ1И)

в интерфейс «Общая шина» (ОШ) и наоборот. При

этом устройства магистралей МПИ и ОШ находятся

в едином адресном пространстве.

Рекомендуется для применения в качестве модуля

обмена данными между микроЭВМ «Электроника 60»

и устройствами с интерфейсом ОШ. Кроме того, адап-

тер может применяться для связи между мини-ЭВМ

«Электроника 100/25», СМ-4 и устройствами с интер-

фейсом МПИ. Реализованы режимы программного об-

мена, прерывания программы и непосредственного до-

ступа к памяти.

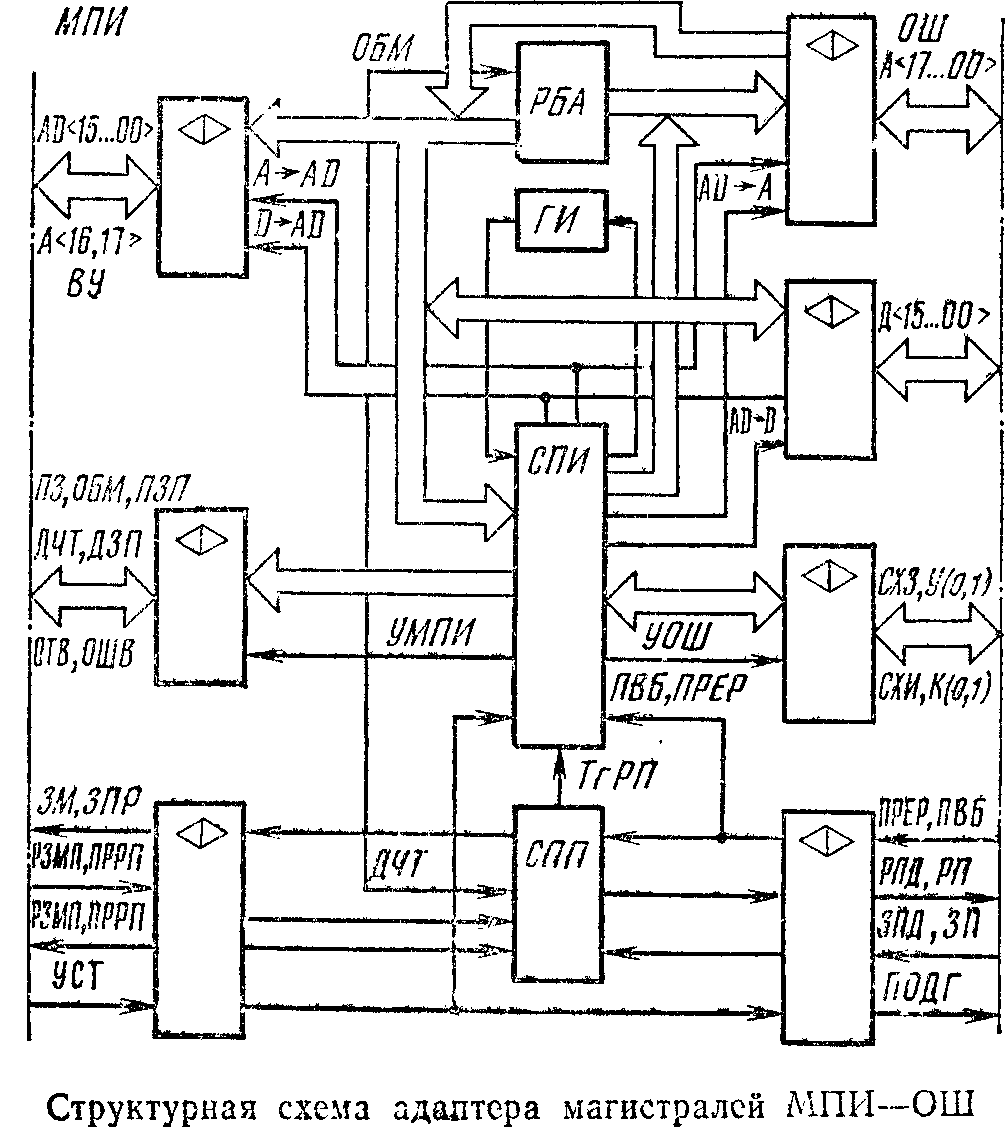

Схема преобразования сигналов интерфейса адапте-

ра выполнена на БИС К1801ВП1-054, что позволило

разместить его на типовой плате микроЭВМ «Электро-

ника 60» размером 135x240x12 мм. Адаптер состоит

из схемы преобразования интерфейсов (СПИ), буфер-

ного регистра адреса (РБА), схемы приоритета преры-

ваний (СПП), двунаправленных усилителей, генератора

тактовых импульсов (ГИ), переключателя выбора ре-

жима (ПВР) (см. рисунок).

Схема СПИ обеспечивает взаимное преобразование

сигналов управления интерфейсов МПИ и ОШ, а также

вырабатывает управляющие сигналы для других узлов

адаптера. Конструктивно схема СПИ выполнена на мик-

росхеме К1801ВП1-054. Регистр РБА хранит адрес на

время обмена при передаче с магистрали МПИ на ОШ.

Регистр РБА программно недоступен и выполнен на

микросхеме К1801ВП-034.

Схема СПП обеспечивает взаимную передачу запро-

сов и разрешений на прерывание между магистралями,

а также трансляцию разрешения на прерывание в ма-

гистраль МПИ при отсутствии запросов на прерывание

в магистрали ОШ.

Двунаправленные усилители предназначены для элек-

трофизического сопряжения внутренних линий с ма-

гистралями МПИ и ОШ. В качестве приемопередатчи-

ков сигналов используется усилитель-формирователь

К531АП2П. Генератор ГИ синхронизирует работу всех

узлов адаптера.

Переключатель ПВР устанавливает режим работы

адаптера. Выбор режима в Зависимости от установки

процессора на магистрали МПИ или ОШ осуществля-

ется переключателем ВДМ1-2 в состояние соответствен-

но «выкл» или «вкл». Ток, потребляемый адаптером,

равен 2,5А.

Конструктивно адаптер выполнен на печатной плате,

устанавливаемой в каркас микроЭВМ «Электроника 60»

или ДВК «Электроника МС 0501». Для подключения

магистрали ОШ на плате установлена вилка СНО

53-60/93-23-В. Питание адаптера осуществляется от

блока питания напряжением 5 В.

Телефон для справок: 532-84-22, Москва.

Сообщение поступило 25 марта 1987 г.

персональные компьютеры

УДК 681.3.06