|

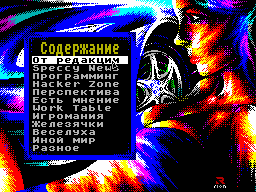

3Bit #01

03 января 2005 |

|

Programming - Non-standard use of the General Sound: Sound emulation coprocessor AY-3-8910.

Non-standard usage

General Sound

(C) Dr.Lion / RSM

The following material is the copyright property! If you use

it refer to the author!

On how many capable sound card

General Sound (hereinafter GS)? Furthermore proigrivaniya

mod'ov sample'ov and she could still many which, if made to

work it a nonstandard way. To do this we need to get a GS its

program, passing control to it and gain full control over

iron-GS. And then the iron is very nehily GS:

Processor: Z80 12MHz

Interrupts: INT 37500Hz

Memory: 128-512Kb (pages on 32Kb)

DAC: 4 channels x 8 bits each

Loudness: 4-channel x 5 bits each

I have long plagued a crazy idea. A

is it possible to create a device based on the Z80,

which could emulate the work of the Muses.

coprocessor AY-3-8910 or YAMAHA analog? Of course you can, but

what should be such a device? It must be software and hardware

is capable of forming the output of the three channels A, B, C.

But for the most conservative estimate the frequency of the

processor device must be at least 14MHz. Even if device I

gather, someone besides me wants to collect it and to its

potsepit old man SPECCY? Who will support the new standard? And

what about people who sit on emulators ZX-SPECTRUM? It was then

that the idea to ispolzavat to emulate AY iron GS. GS is more

or less a standard device and is supported by major emulators

ZX. Although the frequency of CPU GS and less necessary 14MHz,

to put into it a simplified version of the emulator AY still

possible. A few minutes later I would be able to convince you

in this case.

So, let's analyze in detail how

We make resound GS painfully familiar sounds AY. First, let's

be clear what the AY and how it works. AY - this chip, which

contains three generators of rectangular pulses

(Digital tone), noise generator, generator

envelope amplitude registers, shift register

storage device, register the envelope and three DACs.

Tone generator

They represent some schetchikideliteli with preset 12-bit

the division factor and the output digital

tone. Counters, Dividers considered to decrease, and when the

0-th value changes output logic signal to the opposite. Input

frequency for a clock frequency schetchikovdeliteley AY,

divided by 16.

Noise generator

He is, in essence, consists of a counter-divider, and a

similar tone generator device generating pseudo-random output

logical signal. This device is assembled on the shift register

and the element of "exclusive OR". Signal noise generator is

formed like this: clock AY, divided by 16 -> 5-bit counter

divider -> pseudo-random output logic signal.

Generator and the shape of the envelope

Envelope generator consists of a 16-bit counter divider to

the logical output of which is connected 4-bit down counter.

Mode bidirectional counter set register bits form envelope. The

output of down counter formed 4 razryannaya sequence of

amplitudes of the envelope is fed to the mixer first and then

to the DAC.

Registers amplitude

Just as the tone generator are presented for each channel

separately AY. Junior 4-D bit in the register code is the

amplitude and fed to the mixer. Bit 4 - a flag indicating the

mixer to the source amplitude. For 0 - Source younger register

bits of the amplitude at 1 - source code at the output of down

counter generator envelope.

Register mixer

Bits 0-2 enables / disables flow

the mixer output logic signals

tone generator for each channel, bits

5.3 enables / disables the entry into the mixer output logical

pseudo-random signal from the noise generator for each channel

separately. If the logic signal source is 0, then the code of

the amplitude is also equal to 0 if equal to 1, the source code

amplitude is determined depending the flag of the envelope in

case the amplitude.

Digital to analog. Converters

DAC for each channel serves the formation of a mixer codes

amplitude tones, noise and an envelope. These codes are added

and the DAC outputs a certain level of

voltage. It should be noted that the scale

DAC voltage levels AY logarithmic.

Of all the descriptions above toppings AY in GS

There are only TsAP'y, who also have a linear scale output

voltage. Therefore, the missing nodes, we will build

of the specific "building blocks" - teams CPU Z80.

First of all let's define the problem,

to be performed by the emulator AY. Their

just two:

1. The generation of output signals of channels AY.

2. The interpretation of those entering the emulator

input data (in the format of the real

Nogo AY), reconfiguring the emulator.

Ie We must work together

two tasks (the process). And the first of

They should work so that nothing

could interrupt her work, and thus affect the stability and

sound quality - it Problem with absolute priority. Obviously,

that the second task can be performed as

opportunities but we must not forget that

its speed is directly related to

the rate of exchange between the emulator AY and ZX.

Now we will move out reasoning

on iron GS. N1 task should work

processing cycle maskable interrupt

(This type of interrupt available in the GS)

and the problem of N2 - the remainder after treatment

interrupt time. Let's count up the length of

single cycle interrupt GS in bars:

Lgsi = Fgsc / Fgsi

where Lgsi - the length of the cycle interrupt cycle;

Fgsc - clock speed GS Z80 = 12MHz;

Fgsi - interrupt frequency GS = 37500Hz.

Lgsi = 12000000/37500 = 320 cycles

The resulting tsyfry you at first glance, no

what is not said. However, 320 cycles - is 80

elementary commands or 30-35 over-menie

major commands. Out of it, this is not enough to simulate all

the nodes AY. Moreover, the doge to 640 cycles is not enough.

Therefore, for emulation procedure pridetlya allocate 3

interruption of 320 cycles, ie 960 cycles.

During this time, you can calculate all the necessary

components AY. Here is the procedure emulation, suspended for

interrupting:

;------ Procedure for the generation of AY (INT handler in GS)

--- GS_INT EXA; 4 OUT to DAC

EXX; 4

LD A, (# 6000), 13

LD A, (# 6100), 13

LD A, (# 6200), 13

LD A, (# 6300), 13 WorkTime = 60

A_SetA LD DE, # 0000, 10 TONE A

A_NumA LD HL, # 0000, 10

ADD HL, DE; 11

LD (A_NumA +1), HL; 16

A_NumB LD A, # 00; 7

A_SetB ADC A, # 00; 7

LD (A_NumB +1), A; 13

JR NC, B_SetA; 7 / 12

LD A, C; 4

XOR% 00000001; 7 MinTime = 86

LD C, A; 4 MaxTime = 96

B_SetA LD DE, # 0000, 10 TONE B

B_NumA LD HL, # 0000, 10

ADD HL, DE; 11

LD (B_NumA +1), HL; 16

B_NumB LD A, # 00; 7

B_SetB ADC A, # 00; 7

LD (B_NumB +1), A; 13

JR NC, C_SetA; 7 / 12

LD A, C; 4

XOR% 00000010; 7 MinTime = 86

LD C, A; 4 MaxTime = 96

C_SetA LD DE, # 0000, 10 TONE C

C_NumA LD HL, # 0000, 10

ADD HL, DE; 11

LD (C_NumA +1), HL; 16

C_NumB LD A, # 00; 7

C_SetB ADC A, # 00; 7

LD (C_NumB +1), A; 13

JR NC, E_SetA; 7 / 12

LD A, C; 4

XOR% 00000100; 7 MinTime = 86

LD C, A; 4 MaxTime = 96

E_SetA LD DE, # 0000, 10 ENVELOP

E_NumA LD HL, # 0000, 10

ADD HL, DE; 11

LD (E_NumA +1), HL; 16

E_NumB LD A, # 00; 7

E_SetB ADC A, # 00; 7

LD (E_NumB +1), A; 13

JR NC, N_SetA; 7 / 12

LD B, (IX); 19 MinTime = 86

INC LX; 8 MaxTime = 108

N_SetA LD DE, # 0000, 10 NOISE

N_NumA LD HL, # 0000, 10

ADD HL, DE; 11

LD (N_NumA +1), HL; 16

N_NumB LD A, # 00; 7

N_SetB ADC A, # 00; 7

LD (N_NumB +1), A; 13

JR NC, Mixer; 7 / 12

LD A, R; 9

RRCA; 4

LD R, A; 9

JR NC, Mixer; 7 / 12

LD A, C; 4

XOR% 00111000; 4 MinTime = 86

LD C, A; 4 MaxTime = 122

Mixer LD A, C; 4 MIXER

MixVal OR 0 7

LD L, A; 4 WorkTime = 15

AEnFlag LD H, B; 4 / 7 DAC A VALUE

NOP; 4 / 0

LD A, H; 4

BIT 0, L; 8

JR NZ, ASetVo0; 7 / 12

ADD A, H; 4

ASetVo0 BIT 3, L; 8

JR NZ, ASetVo1; 7 / 12

ADD A, H; 4 MinTime = 64

ASetVo1 LD (# 6000), A; 13 MaxTime = 63

BEnFlag LD H, B; 4 / 7 DAC B VALUE

NOP; 4 / 0

LD A, H; 4

BIT 1, L; 8

JR NZ, BSetVo0; 7 / 12

ADD A, H; 4

BSetVo0 BIT 4, L; 8

JR NZ, BSetVo1; 7 / 12

ADD A, H; 4

BSetVo1 LD (# 6100), A; 13 MinTime = 77

LD (# 6200), A; 13 MaxTime = 76

CEnFlag LD H, B; 4 / 7 DAC C VALUE

NOP; 4 / 0

LD A, H; 4

BIT 2, L; 8

JR NZ, CSetVo0; 7 / 12

ADD A, H; 4

CSetVo0 BIT 5, L; 8

JR NZ, CSetVo1; 7 / 12

ADD A, H; 4 MinTime = 64

CSetVo1 LD (# 6300), A; 13 MaxTime = 63

EXX; 4 OTHER

EXA; 4

EI; 4

RET; 10 WorkTime = 22

; MinWorkTime = 732 MaxWorkTime = 817 MidWorkTime = 775 Free =

143-10

By calculating the minimum and maximum time of the procedure

can be established that the period of its launch is 3

interrupts (inside a procedure can not cause an interrupt) is

basic sampling frequency is:

Fgsd = Fgsi / 3 = 37,500 / 3 = 12500Hz

To form one period of the frequency generator tones Fayt

required frequency Sample 2 * Fayt (as in one period

sampling frequency is formed only

a half-Fayt). In our case, the basic sampling rate of 12500Hz,

hence the maximum frequency tone generator is Fgsd / 2 =

6250Hz, ie minimum value of register tones - 18.

(To be continued)

Other articles:

Similar articles:

В этот день... 30 March