В. С. Борисов, А. П. Горяшко

МЕТОДЫ ВСТРОЕННОГО ДИАГНОСТИРОВАНИЯ

МИКРОПРОЦЕССОРНЫХ СРЕДСТВ ВЫЧИСЛИТЕЛЬНОЙ ТЕХНИКИ

Разработка структурных методов встроенного тесто-

вого и функционального диагностирования, ориентиро-

ванных на увеличение среднего времени наработки на

отказ, обнаружение и исправление ошибок, уменьше-

ние времени восстановления отказавшего устройства,

становится необходимым этапом создания перспектив-

ных микропроцессорных средств вычислительной тех-

В программах по развитию микропроцессорных

средств вычислительной техники (МСВТ) заметная

роль отводится проблемам проведения контроля и ис-

пытаний БИС и СБИС при их разработке, производст-

ве и внедрении в микропроцессорные системы. Пока-

зательно также внимание, которое уделяется этим воп-

росам в рамках программы по созданию сверхбыстро-

действующих ИС [1—3].

Резко возросшая функциональная сложность БИС

приводит к чрезвычайному увеличению трудоемкости

получения адекватной математической модели ИС, опи-

сывающей возможные неисправности, предъявляет

очень высокие требования к времени контроля при

традиционных алгоритмах тестового контроля, даже

для регулярных структур типа ОЗУ, делает практичес-

ки неосуществимыми испытания на рабочих частотах.

Необходимость разработки принципиально новых

методов диагностирования на этапе эксплуатации

МСВТ обусловлена стремлением обеспечить высокие

показатели времени восстановления и коэффициента

готовности различных вычислительных и управляющих

систем. Согласно полученным данным около 80% вре-

мени, затрачиваемого на ремонт сложных АСУ, уходит

на поиск неисправностей. На уменьшение этого времени

нацелены методы функционального и тестового дагно-

стирования*.

Система тестового диагностирования (тестового

контроля) предназначена для выработки и подачи на

объект диагностирования специальных тестовых воз-

действий. По ответам от объекта система должна при-

нять решение о его исправности и, возможно, указать

местонахождение неисправного элемента.

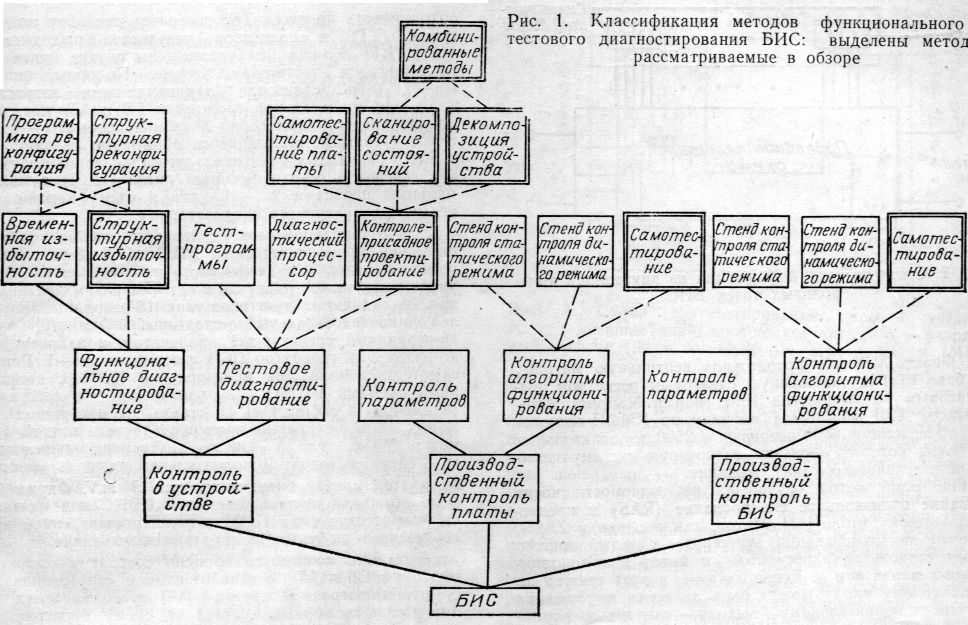

Система функционального диагностирования (аппа-

ратный или схемный контроль) не генерирует специ-

альных тестовых воздействий, но принимает решение об

исправности объекта диагностирования непосредствен-

но в процессе его функционирования, используя избы-

точность, присущую реализуемому устройством алго-

ритму или выходным значениям. Процедуры контроля,

которым подвергается БИС после изготовления, уста-

новки на плату, включения платы в устройство, и ос-

новные способы их реализации показаны на рис. 1.

Рассмотрение методов тестового диагностирования

(ТД) требует изучения способов синтеза тестовой ин-

* Используется терминология, утвержденная

ГОСТ 20911-75 «Техническая диагностика. Основные

термины и определения» и ГОСТ 23563-79 «Контроле-

пригодность объектов диагностирования». Рядом с

тестированными приводятся термины, укоренившиеся

среди разработчиков.

формации. Результаты оценки комбинаторной сложно- I

сти, полученные в последние годы, показали, что боль- j

шинство задач синтеза тестов для произвольных схем

является NP-полными задачами, а возможности каче-

ственного решения подобных задай весьма ограничены. I

Структурные методы тестового диагностирования.

Основное внимание в разработке этих методов уде- |

ляется выбору такой структуры диагностируемого уст- I

ройства, которая существенно облегчает задачу ТД,

т. е. уменьшает не только длину теста при заданной

полноте обнаружения неисправностей, но и трудоемкость

его получения. Идеальная ситуация предполагает воз- I

можность использования стандартного теста, получение

которого вообще не требует знания структуры диагно- I

стируемого устройства.

Структурные методы ТД могут носить «глобальный»

характер. В этом случае синтез автомата (схемы) ори-

ентирован только на оптимальное решение задачи ТД.

При таком подходе и определенных предположениях о i

классах неисправностей возможно построение схем с ]

минимальной трудоемкостью тестирования [4]. Однако

требуемая при этом большая структурная избыточность j!

делает применение глобальных методов на данном эта-

пе развития интегральной технологии проблематичным, j

Более целесообразным представляется использование

«локальных» структурных методов, заключающее в се-

бе попытку при относительно небольшой (10—25%) ]

структурной избыточности существенно уменьшить тру-

доемкость тестирования. В зависимости от величины ]

избыточности можно говорить о двух основных направ- I

лениях развития структурных методов: избыто шость, ]

позволяющая сделать схему более «прозрачной» в тес- j

товом режиме и организовать режим самотестирования, l

Выбор направления практически однозначно опреде-

ляется сложностью исходной схемы: для б< лее слож- |

ных БИС целесообразно обеспечивать режим самотес- |

тирования.

Рассмотрим конкретные схемотехнические решения, J

идя снизу вверх, от уровня отдельных кристаллов до 1

уровня устройств.

Уровень кристаллов. Микропроцессоры (од- I

нокристальные и секционные) имеют сложную схему и

обладают значительными функциональными возможно- 1

стями. Поэтому понятен интерес, проявляемый к ним

как объектам применения структурных методов ТД. ]

Большинство теоретических работ этого плана относит- j

ся к секционным МП, являющимся реализацией фор- 1

мальной модели теории автоматов — одномерной ите- j

ративной решетки. Общие методы модификации итера-

тивных решеток [5] позволяют применительно к конк- ]

ретным типам МП указать рациональные способы вве- 1

дения избыточности. Показано, что реализуя в АЛУ i

каждой секции МП 2901 одну дополнительную функ- j

цию и добавляя схему контроля четности, на которую j

поступают выходные значения этой функции от каждой

секции, можно существенно уменьшить длину обнару- ]

живающего теста, и обеспечить ее независимость от

числа секций МП.

Более детально изучены возможности модификации

однокристальных МП. В работе [6] содержатся сведе- j

ния о сокращении длительности производственных ис-

пытаний 16-разрядных МП 68000 фирмы Motorola за

счет встраивания в схему МП дополнительных схем,

которые в режиме тестирования осуществляют деком-

позицию схемы МП, прежде всего, путем отделения

управляющей части кристалла от операционной. Ут-

верждается, что ценой всего лишь двухпроцентного

увеличения площади кристалла удалось сократить дли-

тельность производственных испытаний одного МП от

нескольких минут до нескольких секунд.

Гораздо полнее вопрос диагностической модифика-

ции однокристального МГ1 рассмотрен применительно к

некоторой модели 8-разрядного МП [7]. Основная идея

модификации состоит в том, чтобы в тестовом режиме

сделать доступным для непосредственного наблюдения

на внешних контактах как можно большую часть ре-

гистров МП и логики устройства управления. Для pea

лизации этой идеи предложена структура, обеспечиваю

щая в тестовом режиме запись (и чтение) во все ре

гистры без выполнения команд МП. Кроме того,

дусмотрена возможность наблюдения в тестовом

режиме за прохождением каждой микрокоманды, бла

годаря реализации двухуровневой памяти микрокоманд

Стоимость подобной структурной модификации, вклю

чающей дополнительные тристабильные элементы, бу

ферный регистр, декодер, набор триггеров и два до

полнительных контакта для выбора тестового режима

не превышает 10% стоимости основной схемы МП

Такое Структурное решение дает возможность относи

тельно просто составить тест-программу, обеспечиваю-

щую обнаружение не менее 95% неисправностей типа

одиночных констант в схеме МП.

Достижения интегральной технологии позволяют

реализовать в виде заказной СБИС или СБИС на базе

вентильной матрицы схемы, размещаемые не так давно

на плате. В этих случаях на кристалле содержится

сложная и функционально не законченная схема, для

которой разработка качественной тест-лрогр,аммы — де-

ло крайне нелегкое, если не безнадежное. Такая ситу-

ация вынудила специалистов по ТД совместно с сис-

темотехниками искать способы проектирования, улуч-

шающие «наблюдаемость» схем. Одна из наиболее из-

вестных попыток подобного рода — метод «сквозного

сдвигового регистра» (ZSSD), предложенный впервые

в работе [8]. Фирма IBM применила этот метод в экс-

периментальной «System 38», выполненной на заказных

БИС, содержащих примерно 800 вентилей. Метод пред-

полагает, что в системе все элементы памяти, за иск-

лючением оперативной, построены как 2-разрядные

сдвиговые регистры, выполненные на двух триггерах-

защелках Z и гг. Триггер Zt предназначен как для ра-

боты в системе, так и для проверки, а триггер г2 ну-

жен только для того, чтобы облегчить процесс тестово-

го диагностирования. Триггер г2 имеет единственный

информационный вход, подключенный к выходу тригге-

ра z 1 и один синхроввод, служащий для переписи со-

держимого в z2. Чтобы объединить такие пары тригге-

ров в единый сдвиговый регистр большой длины, выход

триггера z2 первого каскада соединяют со специальным

входом тест-йнформации (ВТИ) триггера zi втброго

каскада, и так далее до последней пары.

В процессе диагностирования через специальный

вход ВТИ устанавливается начальное состояние регист-

ра, а затем входные наборы поступают на комбинаци-

онные схемы через входные контакты. Сигналы на вы-

ходе комбинационных схем зайоминаются в сдвиговом

регистре. Содержимое регистра может быть считано на

выходе. Отсюда, ТД любой схемы, построенной подоб-

ным образом, оказывается немногим сложнее диагно-

стирования суммы отдельных комбинационных схем.

Схемная избыточность метода ZSSD составляет при-

мерно 20%.

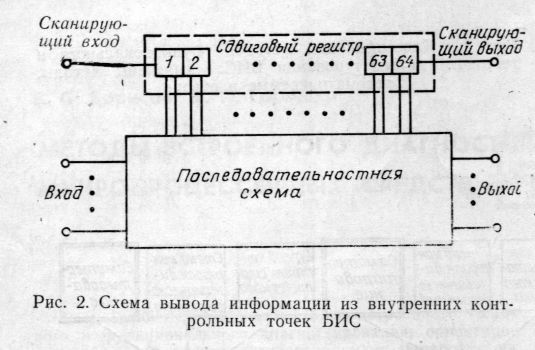

Наблюдаемость схемы может быть улучшена и без

модификации триггерных элементов за счет вывода ин-

формации из заранее выбранных контрольных точек в

сдвиговый регистр, размещенный вне путей прохожде-

ния данных системы (рис. 2). Этот подход был реали-

зован фирмой Spery-Univac под названием Scan-Set [9].

Данные выводились на 64-разрядный сдвиговый ре-

гистр, из которого могли быть последовательно счита-

ны. Фирма Motorola предложила вентильную матрицу

на базе ТТЛШ, снабженную сдвиговым регистром, вы-

полненным по технологии И2Л. Фирма National Semi-

conductor [10] изготовила матрицу по КМОП-техноло-

гии, содержащую 6009 основных и 2500 дополнительных

вентилей, которые образуют встроенную систему испы-

таний и технического обслуживания.

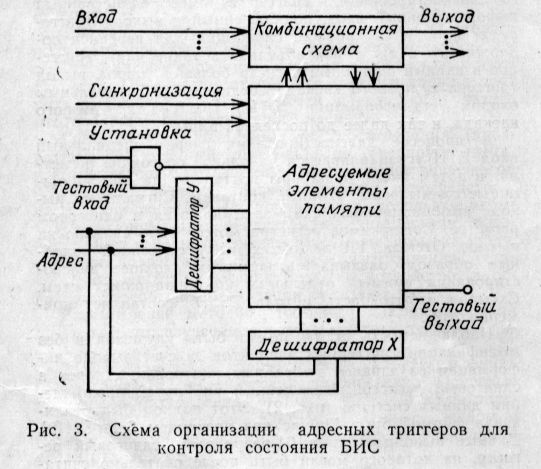

Еще один метод улучшения наблюдаемости носит

название произвольное сканирование (RAS) и предло-

жен фирмой Fujitsu [11]. Метод, так же, как и ZSSD,

основан на модификации триггеров. Каждый триггер

схемы становится адресуемым и имеет два дополни-

тельных входа х и у. Когда х=у= 1, в этот триггер по

специальному входу может быть занесена информация

или по дополнительному выходу — считана информа-

ция. Адресуемые триггеры позволяют представить про-

извольную последовательностную схему в виде, пока-

занном на рис. 3. По задаваемому извне адресу лю-

бой из триггеров схемы может быть установлен в же-

лаемое состояние. Выходные значения считываются на

дополнительных выходах триггеров или на выходе ком-

бинационной схемы. Метод RAS требует трех-четырех

дополнительных вентилей на каждый элемент памяти и

дополнительных схем адресации.

Возросший уровень сложности схем произвольной

логики, размещаемых на кристалле, делает целесооб-

разным осуществление метода самотестирования кри-

сталла. Самотестирование предполагает максимальную

автономность процесса ТД: генератор тестовых воздей- |

ствий (ГТ) и анализатор результата прохождения

теста (AT) должны быть размещены внутри кристалла ;

по периферии . тестируемой схемы. Подобный подход ;

может быть реализован с приемлемыми затратами

лишь при минимальной сложности ГТ и AT, т. е. ког-

да они представляют собой линейные автоматы — сдви-

говые регистры с линейными обратными связями. Из

таких л-разрядных сдвиговых регистров легко получить '

как генератор псевдослучайных чисел (ПСЧ) с макси-

мальным периодом 2 — 1, так и схему хорошо из- j

вестного сигнатурного анализатора.

Для организации самотестирования весьма удобным

оказалось применение схемы BILBO [12] 16-разрядного

регистра, который в зависимости от сигналов внешнего j

управления может работать в четырех разных режимах:

как 16 отдельных триггеров, как 16-разрядный парал-

лелъно-последовательный сдвиговый регистр, как

16-разрядный сигнатурный анализатор, и наконец, как

16-разрядный генератор ПСЧ с периодом 21в—1. Режим

самотестирования для произвольной ПЛМ с несколь-

кими схемами BILBO, размещенными на кристалле, !

рассмотрен в работе [13]. Показано, что при этом ПЛМ

может быть полностью проверена тестом длиной при-

мерно N+m, где А' —- число внутренних коньюнкций,

т—число выходов. Дополнительная площадь кристал- |

л'а в этой случае оценивается как V mN. Фирма Си-

менс объявила о создании новой СВИС под названи- j

ем «самотестируемая ПЛМ с полным выявлением всех i

собственных дефектов и коротких замыканий». |

Тенденции последнего времени состоят в организа-

ции схем ГТ и AT с использованием «внутренних ре- j

сурсов» проверяемой системы [14] путем введения до-

полнительных обратных сязей в схему проверяемого '

кристалла в режиме диагностирования, когда обеспечи- !

вается передача результатов одного цикла проверки с j

выхода схемы на ее вход (кольцевая проверка). При

этом, кроме введения дополнительных обратных связей, ;

необходимы схемы, осуществляющие мультиплексирова-

ние сигналов на входе проверяемой схемы для выбора '

рабочего или диагностического режима. Метод кольце- j

вого диагностирования накладывает определенные ог-

раничения на число запоминающих элементов, необхо-

димых для хранения исходных данных в начале режи- i

ма диагностирования и хранения всех результатов в

конце режима. Если триггеров в проверяемой системе )

недостаточно для реализации этих функций, необходи-

мо вводить дополнительные, функционирующие только

в режиме диагностирования.

Способ ТД, основанный на сочетании метода ZSSD

и схем ГТ и AT, описан в работе [15]. Предложена ор-

ганизация четырех режимов самотестирования, один из

которых полностью совпадает с режимом сканирования

состояний по методу ZSSD. Во втором и третьем режи-

мах проверяются внешние выводы кристалла, т. е. ин-

формация от внешних входов передается непосредст- 1

венно на выход, минуя схему. Наконец, в четвертом

режиме из триггеров схемы образуется сдвиговый ре-

гистр, играющий роль генератора ПСЧ, а результаты

анализируются в 8-разрядном сигнатурном регистре.

Можно заключить, что относительные затраты на

организацию режима самотестирования падают с рос-

том сложности кристалла. По-видимому, полузаказные

схемы на базе вентильных матриц, содержащих 2000 и

более вентилей, являются наиболее подходящим объек-

том для организации методов самотестирования.

Уровень плат. Большинство подходов, рас-

смотренных для уровня кристалла, применимо и на

уровне схемных плат. Однако, большая функциональ-

ная сложность платы и, особенно, функциональная за-

конченность многих типов плат, представляющих со- >

бой, например, микроЭВМ, платы ОЗУ, ППЗУ, процес-

сорные платы, делает наиболее рациональным примене-

ние методов самотестирования.

Для одноплатных микроЭВМ процесс самотестиро-

вания целесообразно организовать как аппаратно-про-

граммный, т. е. с применением схем ГТ и AT, а также

тест-программ, хранящихся в ПЗУ. В качестве ГТ и

AT используются 8-разрядные генераторы ПСЧ и сиг-

натурный анализатор, а тест-программа имеет объем

700 байт и размещается в ППЗУ [16]. Процесс само-

тестирования начинается с генерации теста ядра. При

этом выполняется несколько микрокоманд на специ-

ально выбранных операндах. Затем выполняется тест

встроенных аппаратных средств самотестирования, тест

ПЗУ, тест ОЗУ и т. д. Полнота обнаружения неисп-

равностей (типа константных неисправностей в узлах

схемы) и разрешающая способность предлагаемых

Tcct-процедур зависит от конкретной схемотехнической

реализации метода. По данным работы [16J, около 75%

искусственно введенных ошибок было обнаружено при

реализации режима самотестирования.

Для многоплатной микроЭВМ может оказаться

предпочтительной чисто схемная организация самотес-

тирования [17]. В процессорной плате ГТ реализован

в виде комбинаций 16-разрядного генератора ПСЧ и

детерминированной программы объемом 256 байт, хра-

нящейся в ПЗУ; схема AT содержит 16-разрядный

сигнатурный регистр, мультиплексор, подключающий

сигнатурный анализатор к каждой из 48 контрольных

точек, и ПЗУ эталонных сигнатур емкостью 96 байт.

Объем такого дополнительного оборудования для ор-

ганизации процесса самотестирования составляет при-

мерно 18% от основного, размещенного на процессор-

ной плате. Полный цикл проверки занимает 0,8 с. Пол-

нота обнаружения константных неисправностей узлов

схемы от 70 до 80%. Так же, как и в предыдущем слу-

чае, возможности метода могут быть существенно рас-

ширены, если основная схема, размещаема:! на плате,

проектируется с учетом требований самотестирования.

Уровень модульного устройства. Про-

цесс ТД цифрового устройства, конструктивно реали-

зованного по модульному принципу, может быть орга-

низован при помощи специальных тест-программ, ори-

ентированных на обнаружение неисправности обычно,

с точностью до группы сменных элементов: с примене-

нием диагностического процессора, снабженного соот-

ветствующими тест-программами при шинной органи-

зации системы; методом контролепригодного проекти-

рования устройства, т. е. с использованием диагности-

ческой модификации структуры.

Метод контролепригодного проектирования на прак-

тике может быть реализован тремя способами (см.

рис. 1):

—сканирование состояний дает возможность осу-

ществить поиск неисправности с точностью до кристал-

ла. Если неисправность определяется с точностью до

сменного элемента, то затраты растут пропорционально

числу N сменных элементов в системе. А затраты на

тестирование стандартными методами с той же разре-

шающей способностью растут как 2 ' , где S —число

элементов памяти в сменном элементе;

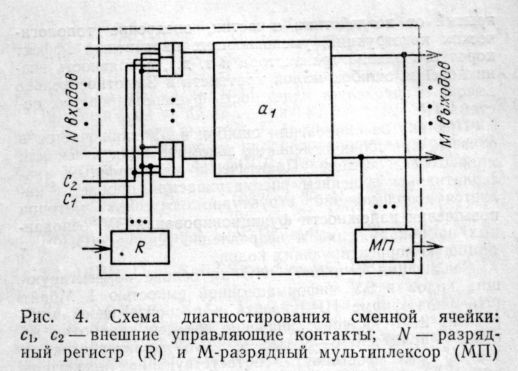

— декомпозиция устройства — разделение системы

в режиме диагностирования на детальные' подсистемы

и проверка каждой подсистемы в отдельности [18].

В качестве подсистемы можно выбрать сменную ячей-

ку (рис. 4). Предполагается, что в режиме ТД все

ячейки могут быть функционально разъединены, напри-

мер, с помощью тристабильных элементов;

— комбинированные способы рационально сочетают

достоинства сканирования состояний и декомпозиции,

например способ, получивший название сканирования

пути (SP), предложенный фирмой Nippon Electric. Он

предполагает модификацию триггерных элементов, в ре-

зультате чего оказывается возможной модификация

сменной ячейки. Примером может служить многопро-

цессорная система TZF 700 System, содержащая

105 ячеек.

Структурные методы ТД для системы должны быть

применимы на любом конструктивном уровне (свойст-

во регулярности) и учитывать принципиальные особен-

ности того уровня, на котором они используются (свой-

ство иерархичности). Например, метод ZSSD является

регулярным и иерархическим, так как позволяет с по-

мощью одного и того же приема — модификации триг-

геров и объединения их в тестовом режиме в сдвиго-

вый регистр организовать проверку кристаллов плат и

Режимы ТД на уровне системы представляют собой

рациональное сочетание методов сканирования, деком-

позиции и самотестирования. В режиме самотестирова-

ния проверяются в динамике отдельные кристаллы, а

в режиме декомпозиции только соединения между кри-

сталлами с помощью небольшого числа тест-кодов [15],

затем в режиме сканирования проверяется плата (смен-

ные элементы) и система в целом. Для организации

автоматического поиска неисправности может потребо-

ваться дополнйтельный диагностический процессор.

Реализация структурных методов ТД на уровне уст-

ройства в целом — задача, охватыван^щан как систем-

ное, так и схемотехническое проектирование.

Структурные методы функционального диагностиро-

вания. Методы функционального диагностирования

(ФД) в сочетании с методами ТД служат эффектив-

ным средством повышения достоверности диагностики

МСВТ. С их помощью контроль правильности функци-

онирования можно осуществлять параллельно с реше-

нием задач. Эти методы наиболее разработаны для

операций пересылок, записи, хранения и считывания

информации, так как они имеют линейный характер и

для них можно применить во всей полноте методы

теории помехоустойчивого кодирования.

В микропроцессорных системах магистрали передач

данных, ОЗУ, ПЗУ составляют от 60% до 30% всех

аппаратных средств. Использование методов ФД толь-

ко для линейных операций уже существенным обра-

зом улучшит надежностные характеристики МСВТ:

увели ит среднее время наработки на отказ за счет

коррекции возникающих ошибок, уменьшит время вос-

становления благодаря возможности локализации мес-

та возникновения неисправности.

Анализ публикаций и технических решений по раз-

витию ЗУ МСВТ показал, что наблюдается тенденция

увеличения информационной емкости всех видов ЗУ:

оперативных, постоянных, внешних. При этом для полу-

чения оптимальных электрофизических характеристик

ЗУ (быстродействие, потребляемая мощность, объем

и т. д.) все чаще используются БИС ЗУ с информаци-

онной емкостью от 16 до 256 Кбит. Несмотря на пред-

принимаемые разработчиками БИС ЗУ меры по увели-

чению надежности и выхода годных (использование

резервных ячеек памяти, применение специальных по-

крытий от воздействия а-частиц, внедрение топологи-

ческих конструкций, уменьшающих паразитный эффект

короткого канала транзистора и т. д.), вероятность воз-

никновения ошибок малой кратности в ЗУ относительно

высока и определяет надежность функционирования си-

стемы [19-21].

Причина возникновения ошибок в ЗУ заключается в

отказах или сбоях отдельных запоминающих ячеек или

микросхем в целом. Практически единственным аль-

тернативным решением рассматриваемой проблемы яв-

ляется использование структурно-логических методов

повышения надежности функционирования ЗУ, основан-

ных на обнаружении и исправлении ошибок (ОНО) с

помощью корректирующих кодов.

Реализация функций ОНО на основе корректирую-

щих кодов в ЗУ информационной емкостью 1 Мбайт

позволила фирме HP указать в паспорте своей мик-

роЭВМ 21МХ высокое значение средней наработки на

отказ — примерно 6—8 тыс. ч. Эта характеристика в

десять раз превышает соответствующие показатели

систем, аппаратно не реализующих функции ОНО,

т. е. ЗУ емкостью 1 Мбайт работает более надежно,

чем, например, стандартный блок ЗУ емкостью

32 Кбайт, изготовленный с применением тех же БИС

ЗУ емкостью 16 Кбит, но не содержащий устройства

ОИО.

В зависимости от реализации различают програм-

мные, аппаратные или структурно-логические и комби-

нированные методы ОИО. Исследования статистики

ошибок в полупроводниковых ЗУ показали, что основ-

ную часть составляют ошибки малой кратности [22].

Для их диагностирования эффективно применение ко-

дов Хемминга, не требующих сложных кодирующих и

декодирующих устройств, обладающих минимальной

избыточностью по сравнению с другими кодами и ма-

лым приращением времени цикла записи и считывания

данных при формировании контрольных соотношений

В ЗУ с информационной емкостью >512 Кбайт це-

лесообразно применять специализированную БИС

ОИО, позволяющую уменьшить составляющую интен-

сивности отказов ЗУ, вносимую блоком ОИО, реализо-

ванным на схемах малой интеграции, минимизировать

число циклов записи и считывания в ЗУ.

БИС ОИО, используемые для ФД, отличаются струк-

турами корректирующего кода, показателями элемент-

ной избыточности, значениями временных приращений

циклов записи и считывания ЗУ, форматами обраба-

тываемой информации, алгоритмами обработки и пере-

дачи данных, возможностями контроля или самоконт-

роля, системами электрических конструктивных и экс-

плуатационных параметров и характеристик.

При практической реализации БИС ОИО применяет-

ся, как правило, модифицированный код Хемминга, ко-

торый не является минимальным, но позволяет унифи-

цировать принципиальную схему кодирующих и декоди-

рующих устройств по числу входов и нагрузок логиче-

ских элементов, уменьшить время задержки

распространения сигнала при формировании контроль-

ных разрядов, синдрома и флагов ошибок, уменьшить

сложность устройства обнаружения многократных оши-

бок, обеспечить увеличение формата информационных

данных путем использования нескольких БИС ОИО,

сохранив при этом минимальный коэффициент избыточ-

ности, осуществить программную обработку синдромов

ошибок и реализовать режим самодиагностики блока

ОИО. Использование встроенных средств ФД [23] дает

возможность организовать оптимальный режим профи-

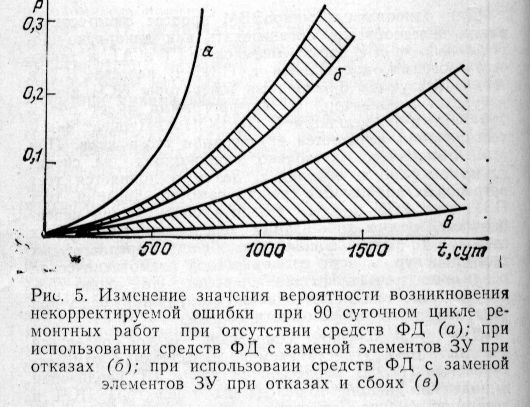

лактических и ремонтных работ (рис. 5).

Достижения микроэлектроники, позволяющие умень-

шить геометрические размеры отдельных элементов

БИС, расширяют функциональные возможности высо-

коинтегрированных БИС ЗУ. Однако уменьшение раз-

меров запоминающих элементов снижает устойчивость

ЗУ к случайным сбоям. Способ борьбы со случайными

сбоями с помощью БИС ОИО, размещаемых на пла- !

тах памяти, для быстродействующих ЗУ оказывается j

неэффективным. Даже самые быстродействующие БИС

ОИО вносят во временную диаграмму ЗУ задержки,

превышающие времена выборки ЭСЛ БИС ЗУ с произ-

вольной логикой.

Эффективный способ решения этой проблемы состо- j

ит в создании ЗУ со схемами исправления ошибок, j

выполненными в составе кристалла БИС (встроенными). ;

Экспериментальные варианты БИС ЗУ с исправлением

ошибок описаны в работах [24, 25].

Создать систему ФД для арифметических и логиче- j

ских устройста значительно сложнее, нежели для уст-

ройств передачи и хранения данных. Можно построить «

корректирующий код, совместимый с арифметическими j

операциями, но такой код будет более сложным по j

сравнению с кодами Хемминга. Арифметические коды

можно разделить на коды, обнаруживающие ошибки и

исправляющие их. Наиболее простыми и распростра- j

ненными являются коды с проверкой по модулю. Ос-

нова создания кода заключается в том, что в его конт- i

рольные разряды записывается остаток от деления ,

исходного кодируемого числа на некоторое заранее ]

заданное число (модуль). Если обеспечить контроль по j

нескольким модулям, то можно обеспечить исправление j

ошибок. Данные коды пока не находят широкого рас-

пространения в МСВТ из-за большой избыточности.

Интенсивно развиваются в теоретическом плане ис- |

следования, посвященные реализации самопроверяемых i

схем встроенного контроля (ССВК) [26]. В принципе

ССВК позволяют в процессе функционирования произ-

вольной схемы обнаруживать любую одиночную неисп- j

равность в момент ее первого проявления. Однако, в

подавляющем большинстве случаев, реализация тако- j

го метода ФД требует 100%-ного усложнения диагнос-

тируемого устройства. Для некоторых типов структур

МСВТ, особенно резервированных систем, экономичес- ]

ки оправданным способом ФД может оказаться дубли- i

рование отдельных узлов системы. Подводя итоги бег- !

лому рассмотрению методов ФД, отметим, что в на- 1

стоящее время лишь для систем передачи и хранения ]

данных имеются практически целесообразные и уже

внедренные методы. Но и для таких систем существу-

ют важные, не до конца проработанные вопросы. Это,

прежде всего, развитие методов ФД для реализации i

реконфигурации в ЗУ путем подключения резервных

ячеек памяти вместо дефектных в процессе изготовле-

ния и эксплуатации.

Проблемы диагностирования на различных этапах :

. жизненного цикла МСВТ, имевшие долгое время второ-

степенное значение, теперь определяют технический уро-

вень разработки. Проектирование МПК и МСВТ без

учета требований контролепригодности оборачивается

значительным замедлением процесса освоения изделий

и увеличением трудоемкости изготовления систем.

Изучение природы задач диагностирования сложных

систем показало, что традиционный путь, состоящий в

разработке тест-программ для систем, спроектирован-

ных без учета требований диагностирования, исчерпал

свои возможности. Определен ряд структурных мето-

дов, которые, оставляя разработчику полную свободу

при решении функциональных задач, существенно уп-

рощают коррекцию, обнаружение и поиск неисправ-

ностей. Поэтому разработка структурных методов

функционального и тестового диагностирования, наце-

ленная на увеличение среднего времени наработки на

отказ (корректирующие коды) и на уменьшение време-

ни восстановления отказавшего устройства (поиск не-

исправного элемента), становится неотъемлемым этапом

проектирования современных МСВТ. До тех пор пока

сохранится тенденция повышения плотности упаковки

кристаллов и увеличения функциональной сложности

схем, размещаемых на одном кристалле, будет расти

интерес к возможностям реализации задач функцио-

нального и тестового диагностирования за счет схем-

ной избыточности. Таким образом, развитие перспек-

тивных МПК и МСВТ будет неизбежно сопровождать-

ся развитием структурных методов функционального и

тестового диагностирования.

ЛИТЕРАТУРА

1. Микропроцессорные комплекты интегральных

схем/В. С. Борисов, А. А. Васенков, Б. М. Малашевич

и др. Под ред. А. А. Васенкова и В. А. Шахнова. — М.:

Радио и связь, 1982. — 192 с.

2. Williams Т. W„ Р а г k е г К. P. Desing for

testability — a survey. — IEEE Trans, comput., 1982,

v. 31, N 1, p. 2—14. '

3. Aviation Week and Space Technology, 19181, v. 114,

N 7, p. 7-—89.

4. Горяшко А. П. О синтезе схем с минималь-

ной трудоемкостью тестирования. — Автоматика и те-

лемеханика, 1981, № 1, с. 145—153.

5. IEEE Trans, on Comput., 1981, v. 30, N 11,

pp. 73—82, 83—94'.

6. Д ж. P. Л а й и б e к. Микропроцессоры с автотес-

тированием. — Электроника. Пер. жури. США «Electro-

nics», 1981, № 25, с. 20-25.

7. FTCS 12th Annual International Symposium

Foult.— Tolerant Computing, 1982, p. 117—127.

8. U. S. Patent, N 3761695, Sept. 25, 1973.

9. Dig. 1977 Semiconductors Test Symp. Oct. 1977,

p. 8—16.

10. Новые разработки изготовителей микрокомпью-

теров. Электроника. Пер. жури. «Electronics», 1983,

№ 7, с. 53-55.

11. Dig. Сотр. Conf. 1980, Feb. 1980, p. 39—46.

12. Proc. 1979, Test. Conf Cherry —Hill. Oct. 1979,

p. 112-119. ■

13. IEEE Trans, on Comput. v. 30, N II, 1981,

p. 146—153.

14. Цзуй Ф. Ф. Испытания in situ — новый метод

проверки быстродействующей БИС/СБИС логики. —

ТИИЭР. 1982, т. 70, № 1, с. 143—165.

15. Комоницки Д. Полное самотестирование си-

стемы — результат синтеза существующих методов. —

Электроника. Пер. журн. «Electronics», 1983, № 5,

с. 26-35.

16. Фазанг М. П. Microbit — способ самотестиро-

вания сложных микрокомпьютеров. — Там же, с. 35—41.

17. Бойкевич А. М„ Горяшко А. П., Миро-

нов В. Г., О р е ш к и н М. И. Синтез легко тестируе-

мых дискретных устройств четвертого поколения.—

Тез. докл. III Международного симпозиума ИМЕКО.—

М.: НТО им. Вавилова, 1943, с. 19.

18. Асафьев Ю. В., Бойкевич А. М., Вол-

чек В. Л., Горяшко А. П. Синтез контролепригод-

ных схем — направление, продиктованное интегральной

технологией. — Изв. АН СССР. Техн. кибер. 1981, № 4,

с. 56—62.

19. Electronic Design, 1982, v. 30, N 3, p. 37, 38.

20. Computer Design, 1982, v. 21, N 1, p. 109—138.

21. Microelectronics and Reliabity, 1982, v. 21, N 6,

p. 775.

22. IEEE J. of Solid-State Crcuits, 1981, v. 16, N 1,

p. 31.

23. Борисов В. С., Горемыкин В. В., Нику-

лин В. С. Микросхема обнаружения и исправления

ошибок в полупроводниковых ЗУ. — Электронная про-

мышленность, 1983, вып. 4, с. 21—23.

24. Б о р и с о в В. С. Полупроводниковое ЗУ с по-

вышенной надежностью функционирования. — Элект-

ронная промышленность, 1979, вып. 5, с. 20—22.

25. Орангзеб Хан. Быстродействующие ЗУПВ

с встроенными схемами исправления ошибок. — Элек-

троника. Пер. журн. «Electronics», 1983, № 18, с. 58—66.

26. Па р х о м е н к о П. П., С о г о м о н я н Е. С.

Основы технической диагностики. — М.: Энергоиздат,

1981, —320 с.

Статья поступила 7 декабря 1983 г.

«АСУ-рейс»

Специалистами МосгортрансНИИпроекта создана

микропроцессорная система управления работой пасса-

жирского транспорта «АСУ-рейс». Эта система состоит

из датчиков, установленных в контрольных пунктах

вдоль маршрута движений; микропроцессор-

ных устройств с дисплеями в кабинах водителей

автобусов; управляющей ЭВМ типа СМ-2М в цент-

ральной диспетчерской.

В случае отклонения от графика движения в каби-

не на экране дисплея появляются цифры: это время

отклонения. Электронный диспетчер по радиоканалу

дальнего действия (20—30 км) подсказывают водителю,

что делать — на экране дисплея появляются команды

ЭВМ-диспетчера, режим движения машины. При рабо-

те системы регулярность движения резко возрастает,

отклонения автобусов от графика не превышают одной

минуты. Если же один или несколько автобусов сошли

с линии, система выравнивает интервалы между ними.

Программисты МосгортрансНИИпроекта разработали

для центральной ЭВМ системы программу «АСУ-рейс».

В память ЭВМ записаны «десятки ситуаций», позволя-

ющие водителю принять верное решение, вызвать тех-

ническую помощь в случае аварии, пожарную машину

при пожаре или скорую помощь для заболевшего пас-

сажира. В Москве по этой программе ЭВМ управляет

движением десятков автобусов.

Подобная микропроцессорная система уп-

равляет движением троллейбусов в г. Воронеже. В ка-

честве ЭВМ-диспетчера служит «Электроника 60».