3. Описание выводов

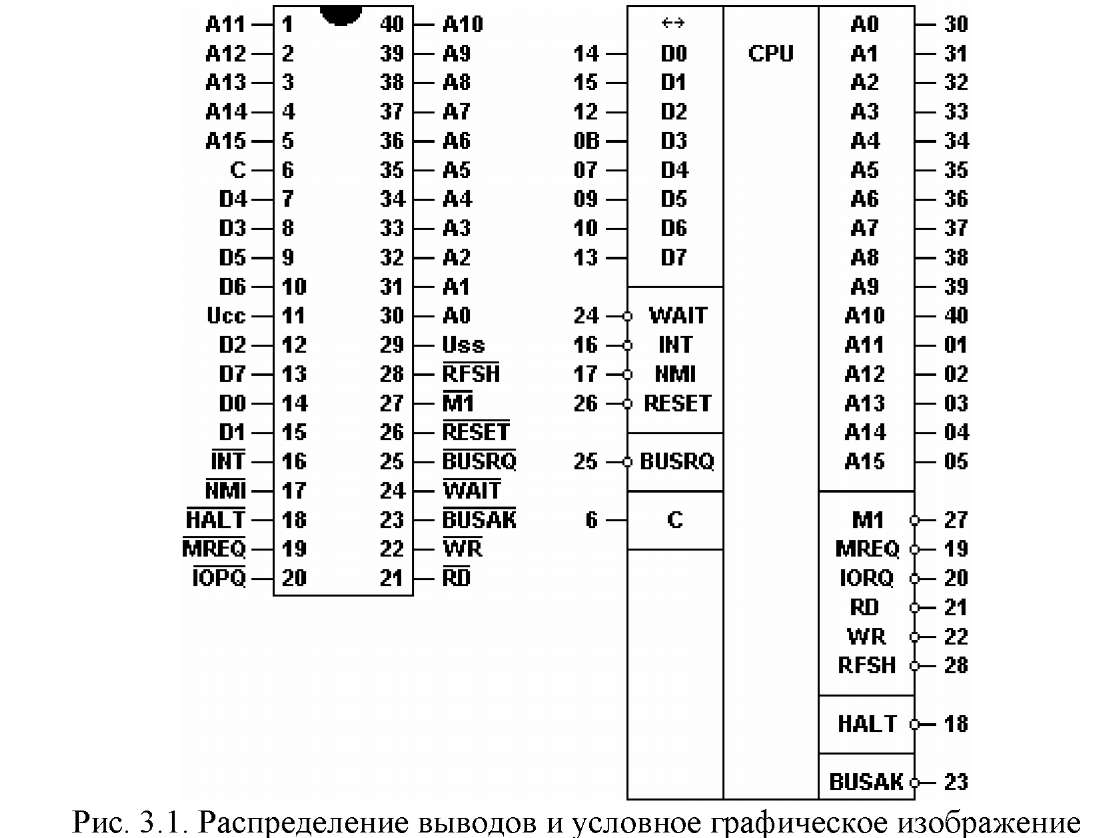

Микросхема Z80 выпускается в стандартном 40 выводном корпусе с двухрядным

расположением выводов типа DIP.

A0.. .A15 Address Bus - Адресная шина

Трёхстабильный выход. Активный уровень - высокий A0-A15 образуют 16

разрядную адресную шину, которая выдает адреса для обмена данными с памятью (64К

максимум) и с устройствами ввода-вывода (65536 каналов максимум). A0 является самим

младшим адресным битом. Во время регенерации ОЗУ 7 младших битов содержат

действительный адрес регенерации.

D0... D7 Data Bus - Шина данных

Трёхстабильный вход-выход. Активный уровень - высокий. D0-D7 образуют 8-

разрядную двунаправленную шину данных, по которой осуществляется обмен данными

между ЦП и памятью, либо между ЦП и устройствами ввода-вывода.

M1 Machine Cycle 1 - Машинный цикл 1

Трёхстабильный выход. Активный уровень - низкий. /M1 указывает, что в текущей

машинном цикле происходит чтение кода операции из памяти. При считывании кода

операции вида CB, ED, DD, FD вырабатывается ещё один цикл M1 для считывания второго

байта кода операции, т.е. сигнал /M1 активизируется дважды.

/M1 также активизируется вместе с сигналом /IORQ в цикле подтверждения

прерывания.

MREQ Memory Request - Запрос памяти

Трехстабильный выход Активный уровень - низкий. Сигнал запроса памяти

указывает системе, что на адресной шине установлен адрес для операции чтения памяти

или записи в память.

IORQ Input/Output Request - Запрос ввода-вывода

Трехстабильный выход. Активный уровень - низкий. Сигнал /IORQ указывает, что

пика адреса содержит адрес внешнего устройства для операции ввода или вывода. Кроме

того, сигнал IORQ генерируется также совместно с сигналом /M1 в цикле подтверждения

прерывания. Тем самым устройству, запросившему прерывание, указывается, что вектор

прерывания может быть помещен на шину данных.

RD Reed - Чтение

Трехстабильный выход. Активный уровень - низкий. Сигнал /RD указывает, что ЦП

выполняет цикл чтения данных из памяти или устройства ввода-вывода. Адресованное

устройство ввода-вывода или память должны использовать этот сигнал для стробирования

подачи данных на шину данных.

WR Write - Запись

Трехстабильный выход. Активный уровень - низкий. Сигнал /WR указывает, что

процессор выдает на ШД данные, предназначенные для записи в адресованную ячейку

памяти или устройство вывода.

RFSH Refresh - Регенерация

Выход. Активный уровень - низкий. Сигнал /RFSH указывает, что младшие 7

разрядов шины адреса содержат адрес регенерации для динамической памяти и текущий

сигнал /MREQ может использоваться для восстановления информации. Примеры

использования сигнала /RFSH см. в книге 7 "Построение систем".

HALT Halt State - Состояние останова

Выход. Активный уровень - низкий. Сигнал /HALT указывает, что ЦП выполняет

команду останова программы и ожидает маскируемое либо немаскируемое прерывание,

чтобы завершить эту команду и начать обработку подпрограммы прерывания. В состоянии

останова ЦП выполняет холостые команды для обеспечения процесса регенерации памяти.

WAIT Halt - Запрос ожидания

Вход. Активный уровень - низкий. Сигнал /WAIT указывает ЦП, что адресованная

ячейка памяти или устройство ввода-вывода ещё не готово к передаче данных. ЦП

генерирует состояние ожидания (холостые такты, в которых не происходит никаких

изменений с ЦП) до тех пор, пока активен этот сигнал. С помощью этого сигнала с ЦП

могут синхронизироваться ЗУ и устройства ввода-вывода практически любого

быстродействия. /WAIT также может использоваться при отладке для реализации

пошагового режима.

INT Interrupt Bequest - Запрос прерывания

Вход. Активный уровень - низкий. Сигнал /INT, формируемый устройством ввода-

вывода, анализируется в конце выполнения текущей команды. Запрос учитывается, если

триггер прерываний (IFF1), управляемый программно, установлен в состояние "разрешить

прерывании", и не активен сигнал /8USRQ

NMI Non Maskable Interrupt - Немаскируемый запрос прерывания

Вход, запускаемый отрицательным фронтом. Фронт запуска активизирует

внутренний триггер NMI. Линия /NMI имеет более высокий приоритет, чем /INT и всегда

распознается в конце выполнения текущей команды, независимо от состояния триггера

разрешения прерываний. /NMI автоматически производит перезапуск (рестарт) ЦП с адрес

66H. Содержимое счётчика команд (адрес возврата) автоматически сохраняется во внешнем

стеке. Т. о. пользователь может возвратиться к прерванной программе.

RESET Reset - Сброс

Вход. Активный уровень - низкий. Сигнал /RESET имеет самый высокий приоритет

и приводит ЦП в начальное состояние:

✓ сброс счетчика команд PC=0000H;

✓ сброс триггера разрешения прерываний

✓ очистка регистров I и R;

✓ установка режима прерываний IM0.

Для корректного сброса сигнал /RESET должен быть активен не менее 3-х периодов

тактовой частоты. В это время адресная шина и шина данных находятся в высокоомном

состоянии, а все выходы сигналов управления неактивны.

BUSRQ Bun Request - Запрос доступа к шине

Вход. Активный уровень - низкий. Сигнал /BUSRQ имеет более высокий приоритет,

чем /NMI и анализируется в конце каждого машинного цикла. Он делает запрос ЦП на

перевод всех его шин в высокоомное состояние для того, чтобы другие устройства смогли

управлять этими шинами (например, при прямом доступе к памяти). Если активизирован

сигнал /BUSRQ то ЦП переводит шины в высокоомное состояние как только завершен

текущий машинный цикл.

BUSAK Bus Acknowledge - Предоставление доступа к шине

Выход. Активный уровень - низкий. Бели был активизирован сигнал BUSRQ, то ЦП

переводит свои шины в высокоомное состояние, как только завершен текущий машинный

цикл. После этого ЦП активизирует сигнал /BUSAK, который сообщает запрашивающему

устройству, что шины адреса и данных, а также трехстабильные сигналы управления

находятся в высокоомном состоянии, и внешнее устройство может ими управлять.

C Clock - Такт

Вход для однофазной тактовой синхронизации. При управлении от ТТЛ-схемы вход

C дополнительно подключается к линии +5В через внешнее сопротивление 330 Ом.

UCC Плюс источника питания

USS Потенциал " земли"