6.3.2. Маскируемое прерывание. Режим О

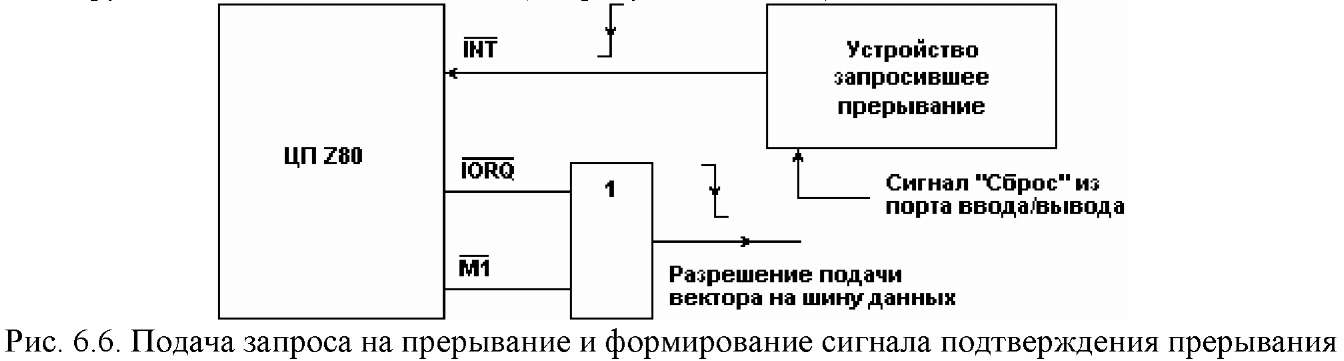

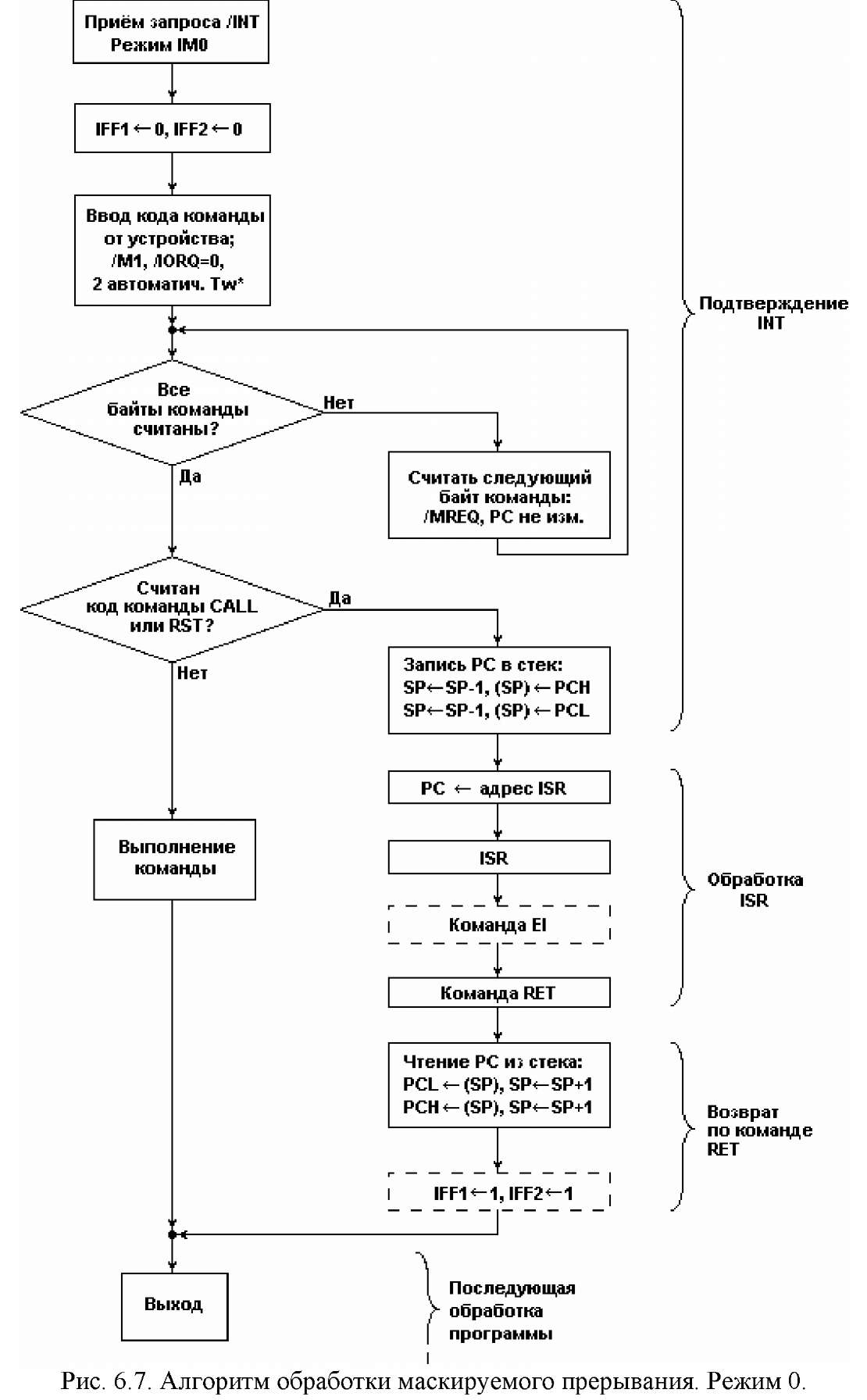

Этот режим аналогичен реализованному в МП Intel 8080. Для него необходима внешняя

вспомогательная логика, которая в случае прерывания подает команду на шину данных ЦП.

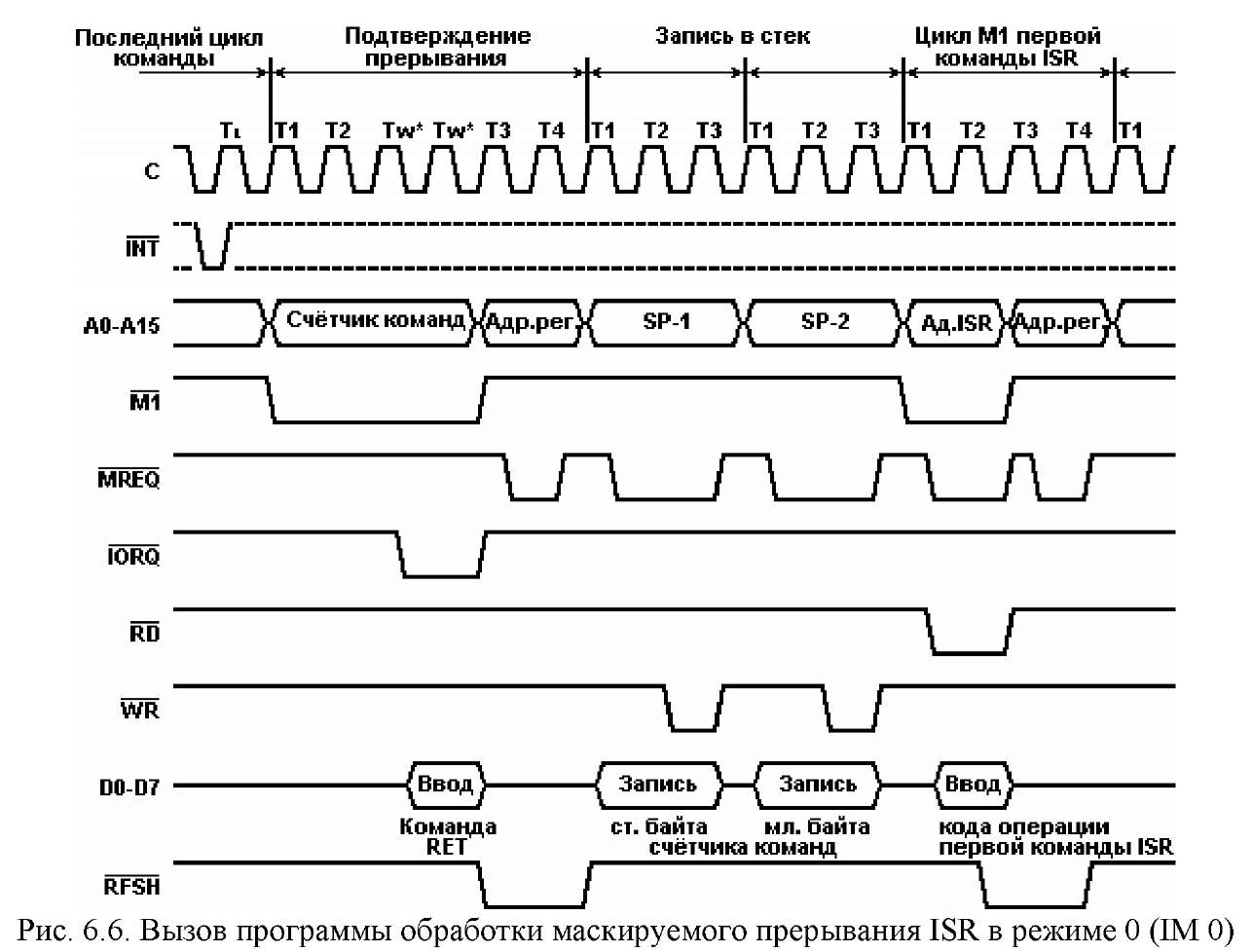

Передача этой команды происходит в цикле подтверждения INTA, когда одновременно

активизируются сигналы /M1 и /IORQ (см. рисунки 4.9 и 6.6).

Т.о. происходит чтение кода операции, но не из памяти, а из прерывающего устройства.

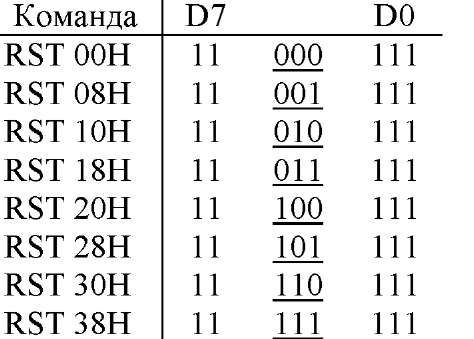

Это может быть любая команду, однако, наиболее эффективно в этом случае использование одной

из восьми команд повторного запуска RST p, где p - адрес рестарта. Для использования этих

команд на ШД должны быть поданы следующие комбинации битов:

Как и для МП I8080, в этом режиме возможно использование контроллера прерываний 8259

(580ВН59). Этот вариант подробно рассмотрен в книге 7.

Режим 0 автоматически устанавливается при выполнении общего сброса, а также

соответствующей командой IMO (Interrupt Mode 0).

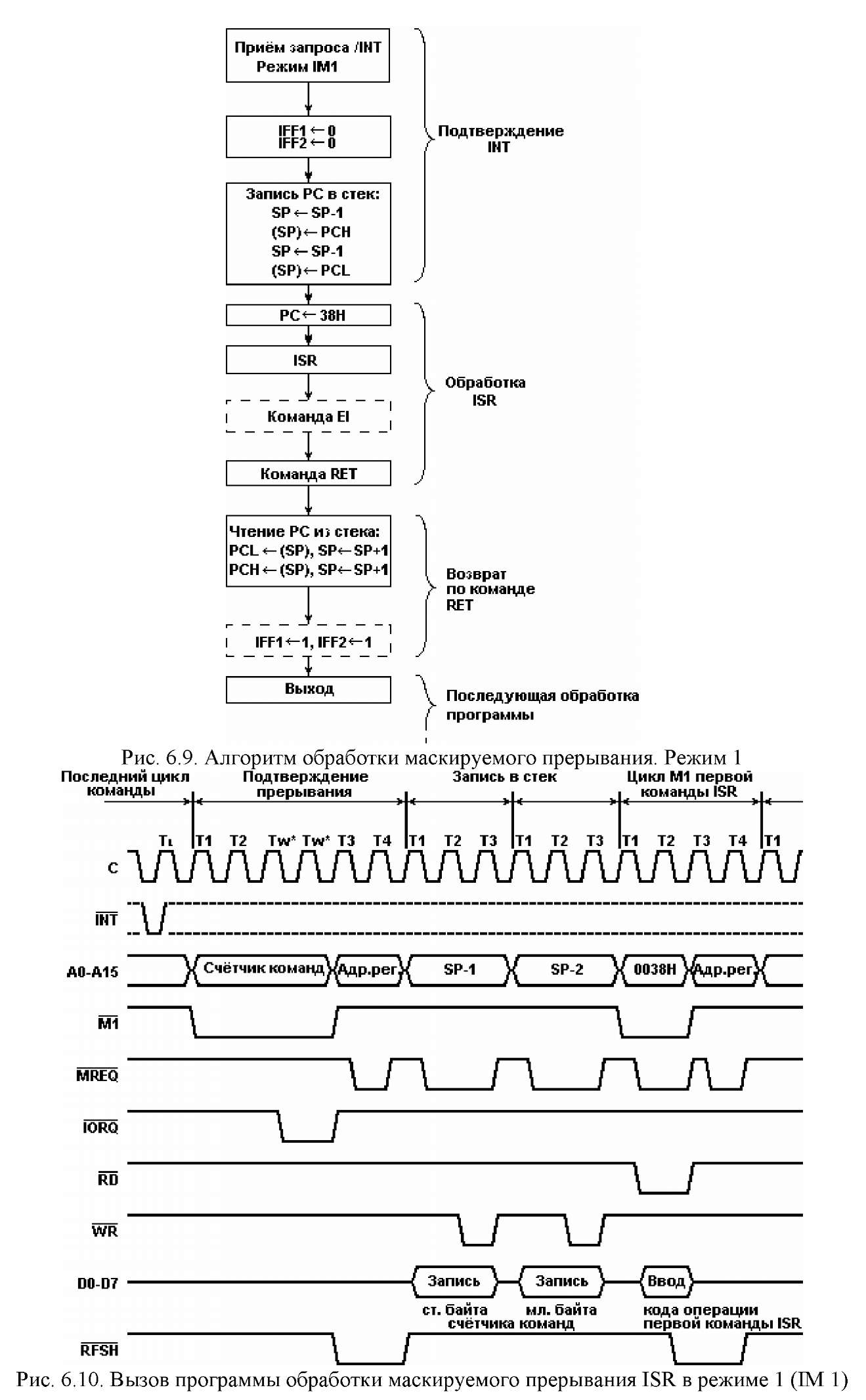

6.3.3. Маскируемое прерывание. Режим 1

Режим прерываний 1 устанавливается командой IM 1. Он применяется в системах с

минимальной конфигурацией, где нежелательно наращивание аппаратной части введением

вспомогательной логики. Обработка сходка с NMI, за исключением того, что вместо адреса 0066H

происходит рестарт к адресу 0038H и цикл подтверждения продлевается на два такта ожидания.

Возврат - по команде RET.

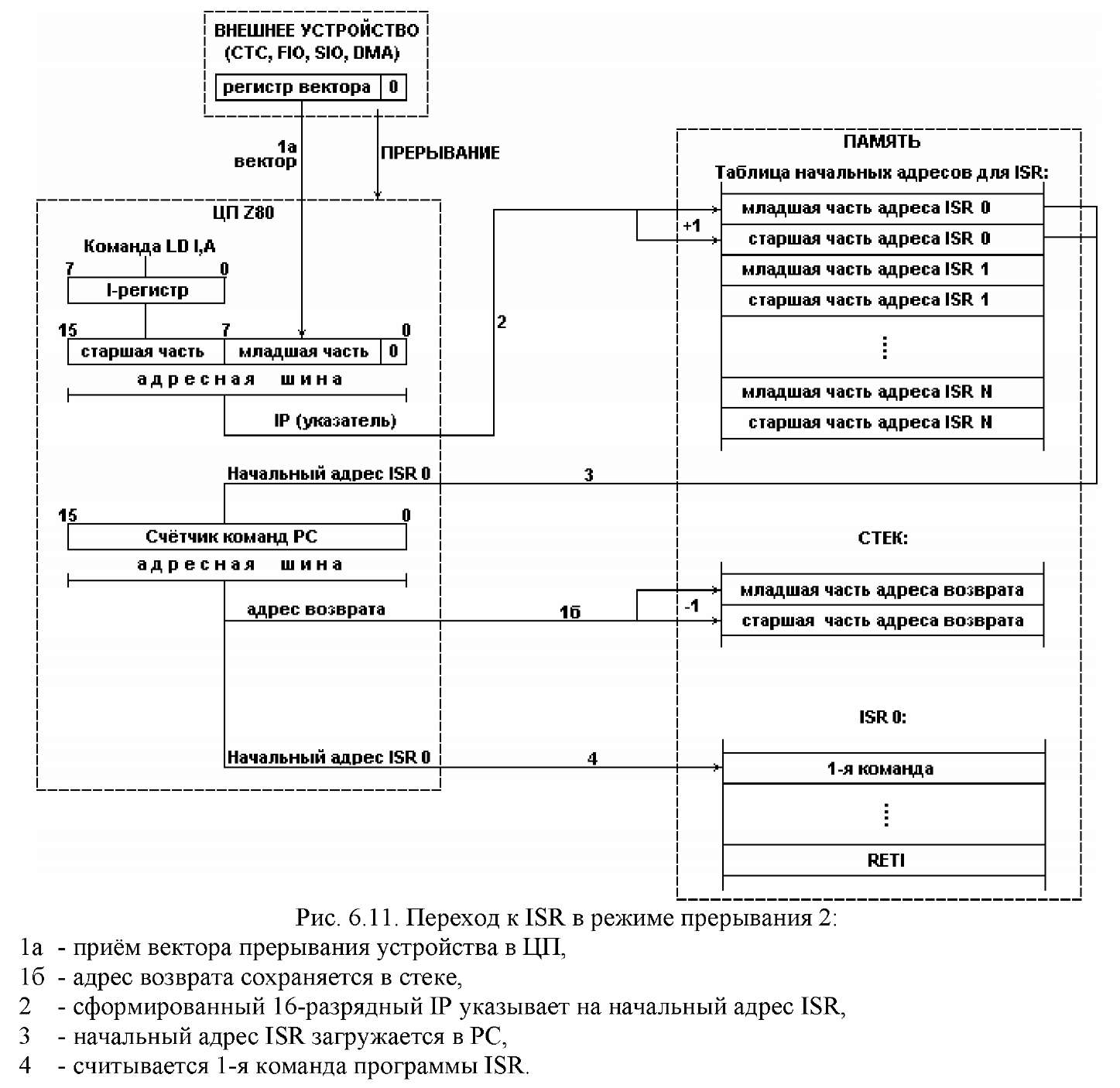

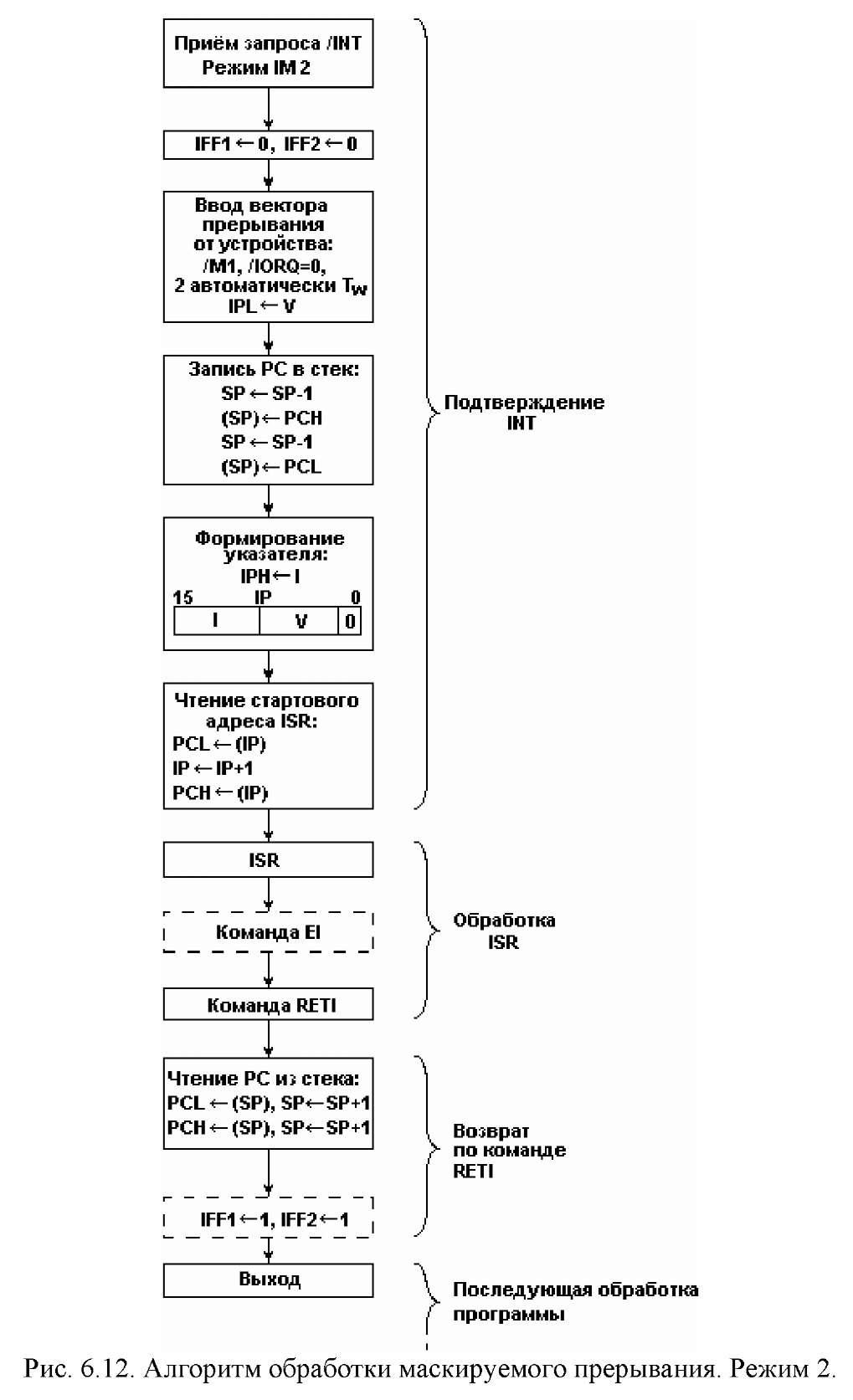

6.3.4. Маскируемое прерывание. Режим 2

Режим прерываний 2 устанавливается командой IM 2. Это самый производительный режим

прерываний микропроцессора Z80. Он применяется в сложных системах с развитой сетью

периферийных элементов. При этом в памяти программируется таблица стартовых адресов

каждой ISR (см. рис. 6.11). Таблица может быть размещена в любой области памяти с

соблюдением лишь правила записи стартовых адресов: младший байт заносится в ячейку с чётным

адресом (A0=0), старший байт в следующую (по возрастанию) ячейку.

В случае приёма прерывания ЦП формирует 16-разрядный указатель IP (Interrupt Pointer)

для выборки стартового адреса нужной программы ISR из таблицы. Для этого прерывавшим

устройством в виде 8 разрядного вектора поставляется младший байт, а старики извлекается из

регистра I микропроцессора. Сформированный таким образом IP указывает на ячейку памяти (в

таблице), где хранится стартовый адрес ISR. Считав этот адрес из двух смежных ячеек, процессор

переходит к обработке программы ISR. Возврат из неё должен происходить по команде RETI. В

целом алгоритм обработки изображен на рис 6.12.

В микропроцессорном комплекте Z80 предусмотрено, что периферийные БИС могут

выдавать в качестве вектора прерывания только чётные байты (D0=0) - для однозначности

адресации ячеек таблицы. Значит, даже при неизменном состоянии регистра I центрального

процессора возможно обслуживание 128-ми устройств в режиме прерываний 2, что во многом

превышает потребности микропроцессорной системы среднего класса.

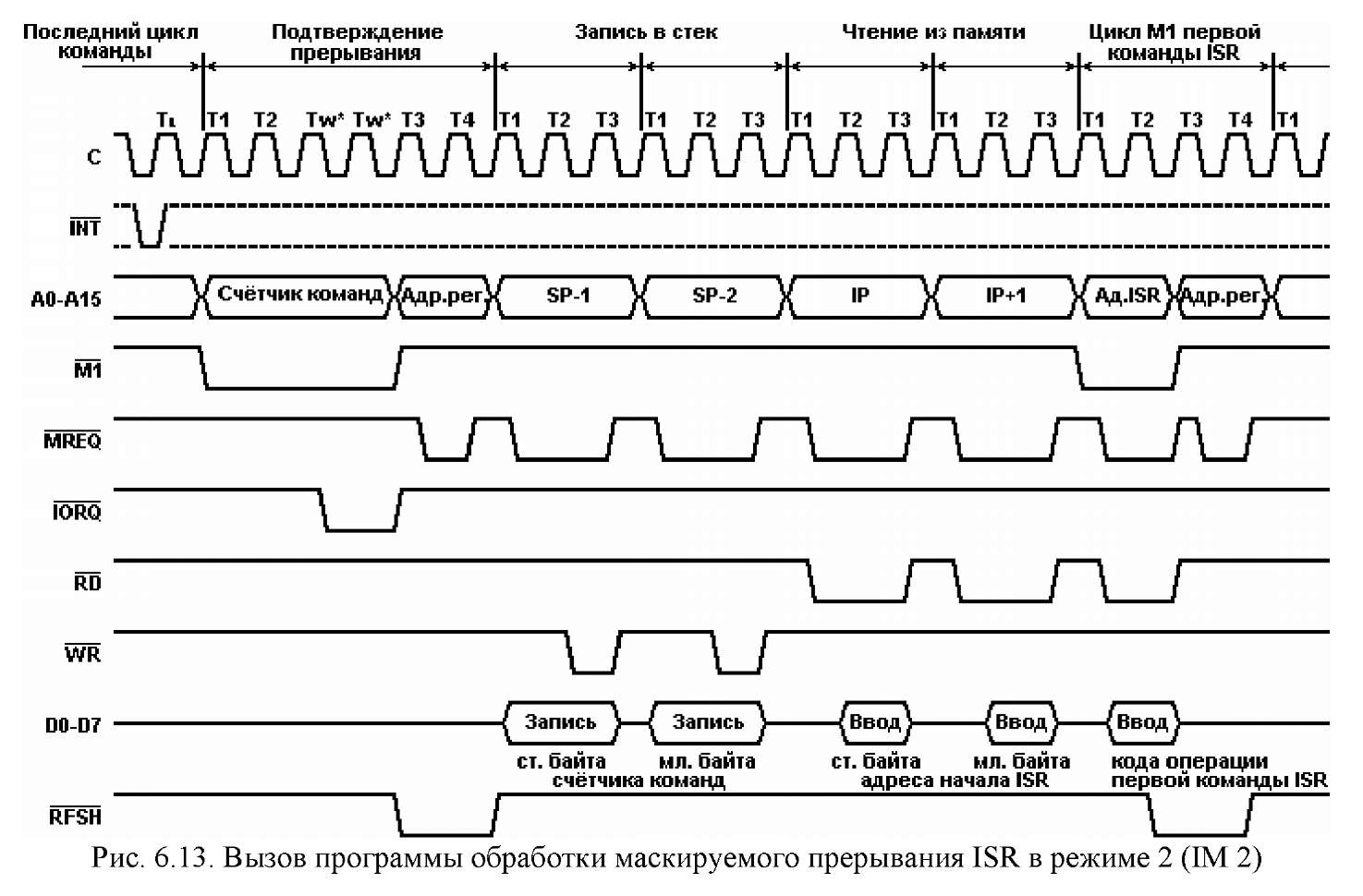

Для перехода к ISR в режиме 2 требуется 19 тактовых периодов (см. временные диаграммы

на рис. 6.13): 7 периодов для ввода 8 разрядного вектора от прерывающего устройства, следующие

6 - для сохранения в стеке текучего состояния PC (адреса возврата), и ещё 6 - для считывания

стартового адреса ISR.

Подробное описание прерываний в системе с полной конфигурацией, особенно, в

отношении периферийных элементов комплекта Z80, а также организации приоритетного

обслуживания см. в книге 7 '^80/Построение систем. Программирование. Отладка".

7. Технические характеристики

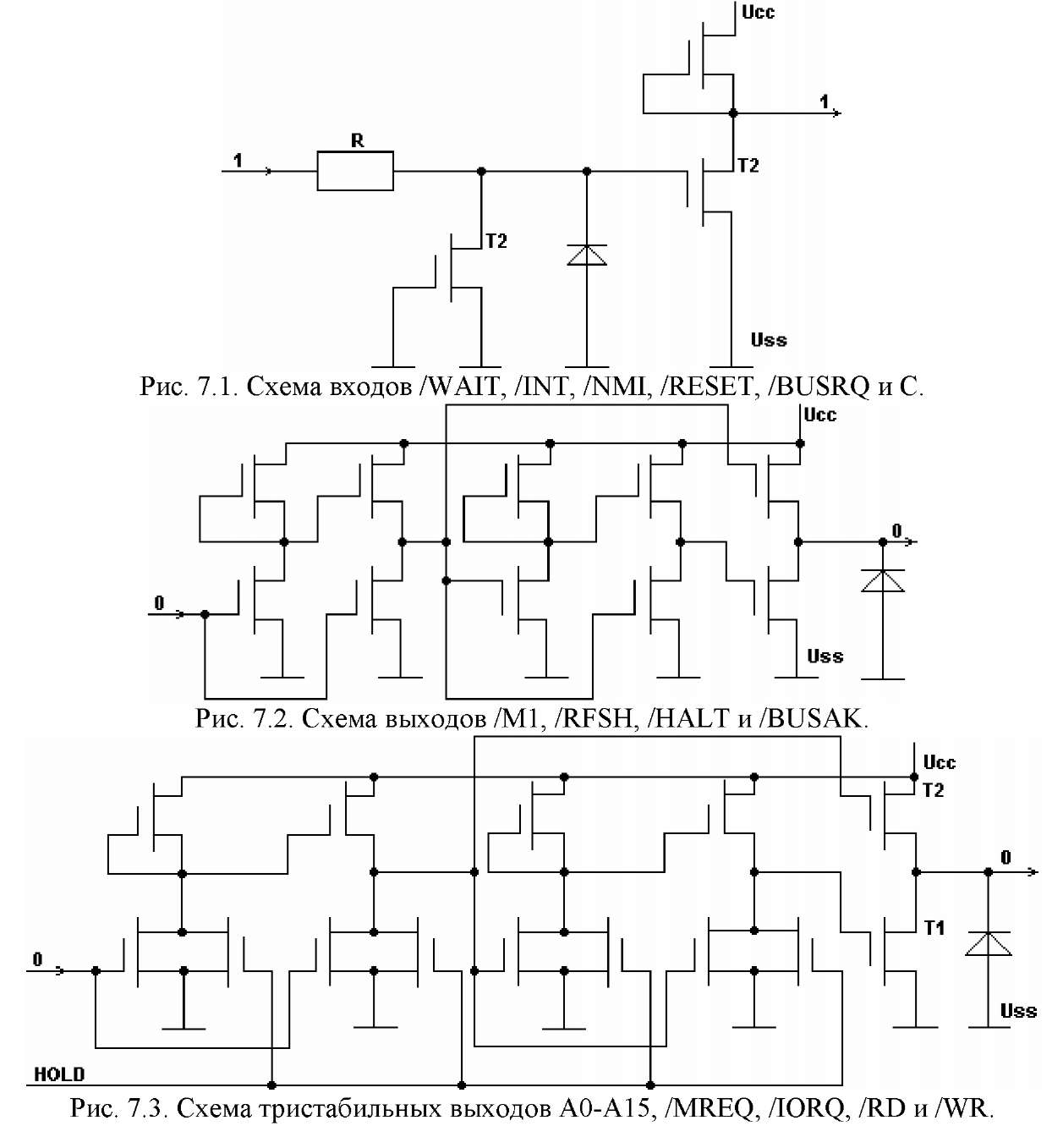

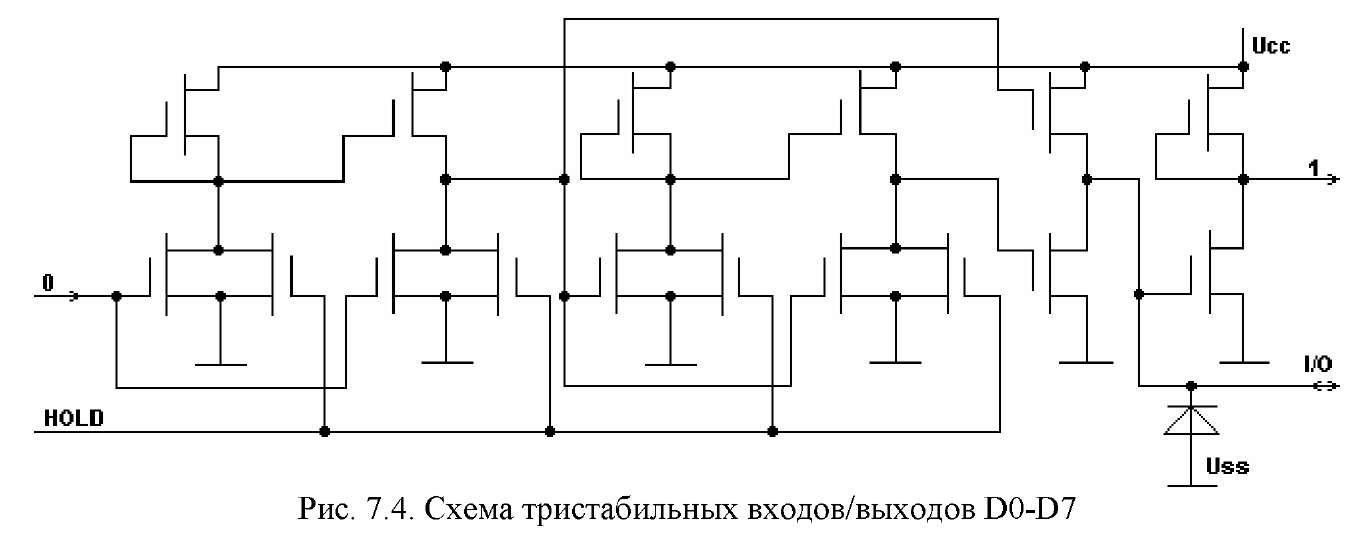

Т.^-Схемы входных и выходных

каскадов

На приведенных ниже схемах приняты следующие обозначения:

I (INPUT) - внешний вход;

0 (OUTPUT) - внешний выход;

1 (input) - внутренний вход;

o (output) - внутренний выход;

I/О (INPUT/OUTPUT) - внешний вход/выход;

HOLD - внутренний сигнал перевода в третье состояние

7.2. Элек^прические и временные

параме^пры/.