Р. А. Лашевский, Э. Э. Тенк, В. С. Хорин

ОДНОКРИСТАЛЬНОЕ СТАТИЧЕСКОЕ ОЗУ

СО ВСТРОЕННЫМ ИНТЕРФЕЙСОМ

Применение усовершенствованной л-канальной тех-

нологии с минимальным топологическим размером

2,5 мкм позволяет перейти к выпуску однокристальных

блоков памяти со стандартным интерфейсом типа Ин-

тербис и большим запасом устойчивости в рабочем ди-

апазоне температур от —60 до +85°С при допустимом

отклонении напряжений питания -^-10%.

Микросхемы статических ОЗУ емкостью

16 Кбит имеют одноразрядную (16КХ1) или

байтовую- (2КХ8) организацию. Первые пред-

назначены для построения ОЗУ относительно

большой емкости — более чем 16 К слов, вто-

рые — для ОЗУ емкостью 2К--16К 8-,

16-разрядных слов.

16-разрядные микроЭВМ с однокристаль-

ным процессором, как правило, имеют единую

внутреннюю магистраль передачи информа-

ции. Структура магистрали определяет интер-

фейс блока ОЗУ, т. е. совокупность адресных,'

информационных и управляющих шин, для

которых задана временная диаграмма движе-

ния сигналов. В большинстве отечественных

16-разрядных микроЭВМ принят интерфейс

типа Интербис*, отражающий характерное

для БИС ограничение по числу выводов (ад-

рес и информация передаются по одним и тем

же шинам с разделением во времени).

Блок ОЗУ 16-разрядной ЭВМ, построен-

ный на микросхемах, статического ОЗУ с бай-

товой организацией, должен содержать, кро-

ме микросхем ОЗУ, большое число микросхем

малой и средней степени интеграции для реа-

| лизации интерфейса блока, обеспечивающего

связь с общей шиной. Дополнительные микро-

* Проблема внутриплатного интерфейса в микропро-

цессорных системах /М. П. Гальперин, В. В. Городец-

i кий, А. Ф. Дриапак, В. Н. Огинский. — УСиМ, 1982,

■ № 6, с. 17—24.

схемы выполняют функции мультиплексиро-

вания линий шины, дешифрации кодов, выбо-

ра кристалла в поле памяти. Эти микросхемы

в значительной мере определяют размеры и

трудоемкость изготовления одноплатных мик-

роЭВМ.

Развитие технологии и увеличение степени

интеграции n-канальных БИС позволяют пе-

рейти к выпуску качественно новых микро-

схем — однокристальных блоков памяти для

микропроцессорных средств вычислительной

техники. К их отличительным особенностям

относятся многоразрядная организация, соот-

ветствующая разрядности микропроцессорной

системы, и наличие встроенных аппаратных

средств, обеспечивающих подключение блока

к общей-Шине системы без дополнительных

микросхем.

Микросхема К1809РУ1 представляет собой

блок статического ОЗУ с организацией 1024

16-разрядных слов и интерфейсом Интербис.

Микросхема работает в режимах записи и

считывания 16-разрядного слова, записи стар-

шего или младшего байта, считывания и запи-

си слова по одному адресу, считывания слова

и записи байта по одному адресу, хранения

информации.

В состав блока ОЗУ входит программиру-

емое устройство для дешифрации 5-разрядно-

го кода сигнала выбора кристалла, содержа-

щее 5-разрядный регистр и схему сравнения.

Доступ в регистр осуществляется по опреде-

ленному адресу FFFO. Устройство позволяет

обойтись без внешнего дешифратора, если к

общей шине присоединено несколько блоков

памяти, а также изменять положение храня-

щегося в блоке массива информации в адрес-

ном поле микроЭВМ.

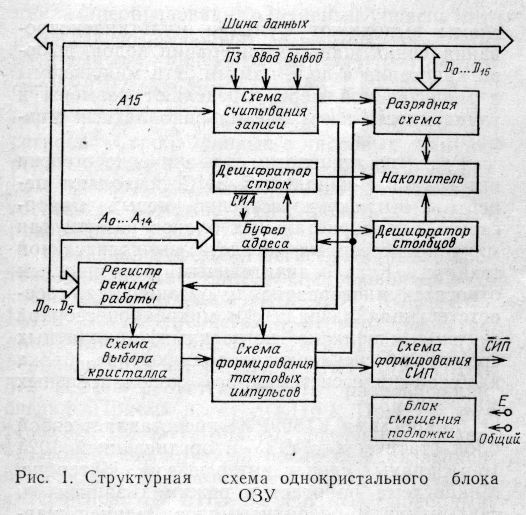

В состав микросхемы входят накопитель

информации, дешифратор строк, дешифратор

столбцов, разрядная схема (PC), схема фор-

мирования синхроимпульса памяти (СИП),

буфер адреса, схема формирования тактовых

импульсов, схема управления считыванием —

записью, схема выбора кристалла, регистр ре-

жима работы, блок смещения подложки

(рис. 1).

При медленно меняющемся входном сиг-

нале компараторов в зоне порога переключе-

ния появляются осцилляции. Их исключают

стандартными методами — вводя гистерезис

!с помощью положительной обратной связи.

ЛИТЕРАТУРА

1. Шило В. Л. Функциональные аналоговые ин-

тегральные микросхемы. М.: Радио и связь, 1982.

2. Мячев А. А., Никольский О. А. Стандарт-

ные интерфейсы микропроцессорных систем. — Микро-

процессорные средства и системы, 1984, № 1, с. 27—33.

3. Устройство параллельного обмена И1. Техническое

описание и инструкция по эксплуатации, 1977.

4. А л е к с е н к о А. Г., К о л о м б е т Е. А., С т а-

родуб Г. И. Применение прецизионных аналоговых

ИС. М.: Радио и связь, 1981.

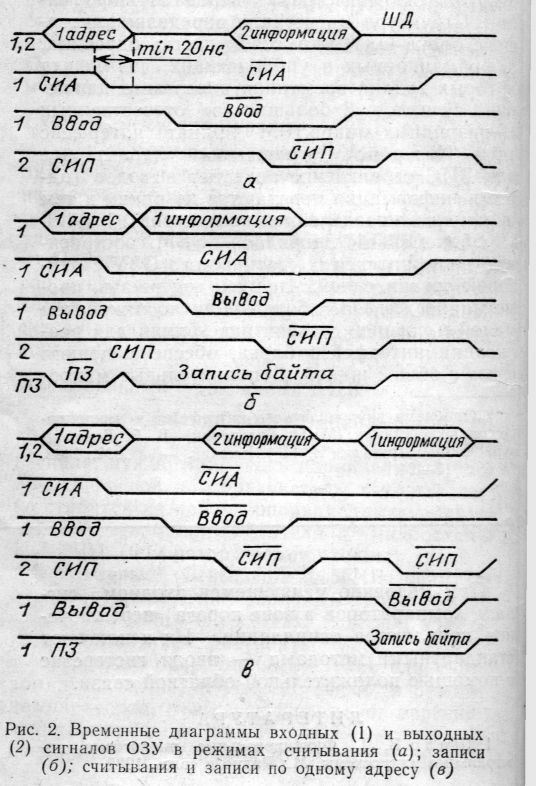

Общая шина содержит совмещенные ли-

нии адрес — данные (адрес Ао—А14) данные

До—Д15), а также линии управляющих сигна-

лов. Сигнал ВВОД свидетельствует о готовно-

сти ведущего устройства принять информа-

цию. Сигнал СИП осуществляет синхрониза-

цию памяти, и означает, что данные с шины

приняты, сигнал СИА свидетельствует о нали-

чии на входах достоверного адреса, сигнал

ВЫВОД — о том, что на шине достоверная

информация. Отдельный сигнал ПЗ определя-

ет переход в режим записи байта.

В режиме записи словачкод адреса посту-

пает в буфер адреса. Одновременно на вход

ПЗ приходит сигнал «Лог. 1» (низкий уро-

вень), который задерживает выдачу адреса

на дешифраторы до прихода сигнала В"ЬЬ

ВОД. По сигналу ВЫВОД и отсутствию за-

прета записи начинают работать дешифрато-

ры, информация проходит через разрядную

схему и поступает в выбранную ячейку.

В режиме записи байта на вход микросхе-

мы ПЗ поступает дополнительный сигнал

ЗАПИСЬ БАЙТА. По сигналу ВЫВОД, от-

сутствию запрета записи и в зависимости от

признака старшего или младшего байта (15

разряд адреса) — происходит запись байта в

накопитель информации. Сигнал «Лог. 1» со-

ответствует записи старшего байта. По окон-

чании процесса записи в ячейку памяти фор-

мируется сигнал СИП, прерывающий сигнал

ВЫВОД. После окончания сигнала СИА вы-

вод схемы СИП переходит в состояние высо-

кого сопротивления.

В режиме считывания код адреса поступает

в адресный регистр и держится на шине дан-

ных 20 не после прихода сигнала СИА. При

наличии соответствующего кода выбора кри-

сталла код адреса поступает в дешифраторы,

которые выбирают нужную ячейку памяти.

После поступления информации из ячейки в

разрядную схему начинается предзаряд шин

дешифратора и матрицы.

После поступления сигнала ВВОД инфор-

мация выдается на шину данных, одовремен-

но формируется сигнал СИП. По окончании

сигнала ВВОД выход PC переходит в состоя-

ние высокого сопротивления, сигнал СИП

сбрасывается в состояние «Лог. 0». После

окончания сигнала СИА вывод схемы СИП

переходит в состояние высокого сопротивле-

ния.

Режим чтения и записи слова по одному

адресу аналогичен чтению и последующей

записи в ЗУ; отличия заключаются лишь в

том,, что адрес и сигнал ПЗ выставляются

только перед считыванием, а сигнал СИА не

прерывается между считыванием и записью.

При работе микросхемы в режиме считывания

слова и записи байта на вход ПЗ поступает

сигнал ЗАПИСЬ БАЙТА. Быстродействие

микросхемы определяется временем считыва-

ния или записи информации (300 не) и дли-

тельностью цикла записи или считывания (не

более 400 не). Эти данные относятся к емко-

сти нагрузки 100 пФ и рабочему диапазону

температур от —60 до +85°С. Микросхема

требует одного источника питания +5 В с

допустимым отклонением напряжения ±10%.

Потребляемая от источника мощность состав-

ляет не более 400 мВт. Встроенный в кри-

сталл блок смещения выдает напряжение

смещения подложки около —1,7 В.

Указанные характеристики однокристаль-

ного блока памяти получены благодаря при-

менению усовершенствованной п-канальной

технологии с минимальным топологическим

размером 2,5 мкм. Эффективная длина кана-

ла транзистора составляет 1,8 мкм, толщина

затворного диэлектрика — 55 нм. Выбором

соответствующей подложки и дозы легирова-

ния удалось минимизировать эффекты корот-

кого канала. Это обстоятельство и использо-

вание нагрузочных транзисторов со встроен-

ным каналом позволило получить большой за-

пас устойчивости в широком диапазоне темпе-

ратур при 10%-ном допустимом отклонении

напряжений питания.

Запоминающий элемент площадью менее

900 мкм2 представляет собой статический

триггер с четырьмя транзисторами и двумя

резисторами из поликристаллического крем-

ния. Площадь кристалла, содержащего 102

тысячи элементов — транзисторов и резисто-.

ров, — около 25 мм2. Построение микросхемы

в виде однокристального блока и 16-разряд-

ная организация потребовали 3—4 мм2 допол-

нительной площади кристалла. Совмещение

шины адреса и данных дало возможность по-

местить микросхему в 24-выводной корпус со

штыревыми выводами. Микросхема К1809РУ1

может применяться с наибольшим экономиче-

ским эффектом в микроЭВМ малых конфигу-

раций, представляющих собой управляемую

однокристальным микропроцессором внутрен-

нюю магистраль, к которой присоединены

микросхемы ОЗУ или ПЗУ (РПЗУ), выпол-

ненные в виде однокристальных блоков, а

также несколько однокристальных блоков

связи с внешними устройствами. Такие мик-

роЭВМ могут состоять только из БИС, без

дополнительных ИС или СИС (за исключени-

ем микросхем усилителей для организации

внешнего интерфейса ЭВМ).

По типу корпуса и схеме разводки выво-

дов микросхема К.1809РУ1 аналогична мик-

росхеме ПЗУ с масочным программировани-

ем К1809РЕ1 и электрически программируе-

мому РПЗУ с УФ-стиранием К573РФЗ. Со-

гласование разводки выводов этих трех мик-

росхем позволяет унифицировать печатную

плату для различных модификаций микро-

ЭВМ, отличающихся набором типов ЗУ и

объемом хранящейся в них информации.

Статья поступила 27 марта 1984 г.

ВСЕСОЮЗНАЯ КОНФЕРЕНЦИЯ

«МИКРОПРОЦЕССОРНЫЕ СИСТЕМЫ»

С 16 по 19 мая 1984 года в Челябинске проведена

Всесоюзная научно-техническая конференция «Микро-

процессорные системы».

Работа конференции проходила по трем секциям:

«Архитектура, математическое и программное обеспече-

ние микропроцессорных систем», «Оценка эффективнос-

ти микропроцессорных систем и методы обеспечения их

надежности», «Применение микропроцессорных систем».

Доклады, прочитанные на первой секции, охватыва-

ют практически все основные проблемы общетеоретиче-

ского и прикладного характера: структурное програм-

мирование, моделирование вычислительного процесса,

методы и средства распараллеливания решающих про-

цедур и т. д.

Особо следует отметить направления, связанные с

концепцией базового кристалла, однородными специали-

зированными микропроцессорными системами, система-

ми автоматизации программирования микропроцессоров.

Этим вопросам было посвящено несколько пленар-

ных докладов, в частности Г. А. Никитина и А.-С. Бо-

кова «Параллельно-ассоциативные микропроцессорные

системы», С. Т. Хвоща «Мультиплексные каналы — ос-

нова для построения специализированных микропроцес-

сорных систем». Среди стендовых докладов можно от-

метить доклад Н. Г. Суковатова «О новых программных

системах для обработки изображений», Р. В. Шмитаса

«О средствах построения ассемблеров с обозначениями,

задаваемыми пользователями» и другие. Большой ин-

терес участников конференции вызвали стендовые док-

лады С. Т. Хвоща «Современное состояние разработок

микропроцессорных систем» и С. С. Булгакова «О но-

вых БИС в серии К1804».

Доклады, прочитанные на второй секции, были по-

священы оценке эффективности микропроцессорных сис-

тем, вопросам диагностики и отладки устройств с мик-

ропроцессорным управлением.

Наибольший интерес вызвали доклады, прочитанные

на третьей секции по применению микропроцессорных

средств и систем в различных областях народного хо-

зяйства страны: от традиционно использующих средст-

ва вычислительной техники в системах управления, про-

ектирования, диагностики до сельского хозяйства, энер-

гетики, телеобработки, в учебных процессах и других

областях науки и техники. В частности, доклады

Г. И. Каплуна «О системе управления электроприводом

робота на базе микроЭВМ», С. В. Воротинцева «Разра-

ботка контроллеров различных устройств» и другие.

В целом работа конференции способствовала .уста-

новлению деловых контактов между представителями

различных специальностей.

Ю. С. Смирнов, Ю. Н. Чернышев

УДК 681.325.5+681.326—181.4