|

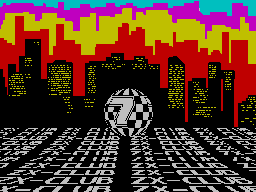

ZX Club #07

28 февраля 1998 |

|

Hard group - Expansion of computer memory, "Synthesis of 2 'to 128 KB.

(C) 1997 PREDATOR / FAST Group The expansion's capacity, "Synthesis of-2" to 128kb. Recently, users sorokvosmyh machines may have noticed that they have are very few new programs. And, Of course, this is associated with memory. So as I once had a 48Kb-computer, I consider it my duty to share with all experience, so lost as a result Spectrum was unsuccessful experiments as little as possible. Thus, we have in common the following models Speccy: Leningrad-1, Companion-2 (I have even Kompanon1) Synthesis of 2 (he is, my dear, this little black ...), Synthesis-M. All these models are 48k. In Revue ZX-94 / 4 was the following article on the topic expansion of Leningrad to 128 kilobytes, so that users who are friends with a soldering iron can safely extend their components for the scheme. With companions and other domestic distortions on the basis of the PLA to complicated, but in Review 95 / 5 (or 6) was even scheme. I Synthesis of 2, and I will tell you how right to extend this comp. But first a little theory. Spectrum-128 has a system port # 7FFD. The layout of bits is as follows: D0-D2 - the page number at # C000 # FFFF. D3 - switch screens (0 - screen 5th bank 1 - 7th). D4 - 0 - ROM-128, 1 - ROM-48. D5 - a complete blockage of the system port to a hardware reset. D6, D7 - in the original machine is not used, but in Russia these bits rather often expand the memory up to 256 or 512 kilobytes, not enter the second system port. The very extended memory management scheme consists of the following parts. In parentheses number of chips for schemes to enhance Synthesis: 1) directly to the port itself, usually built on the trigger TM9 or register IR22 or on these chips (DD1). 2) decoding scheme is the port # 7FFD (or truncated addresses # FD). Collected in shallow logic, provides a readout Register with the data bus at the right time. Not decodes when the fifth bit System Port (DD3.1-3, DD4.1). 3) multiplexer. Ensures proper operation of the memory. At # 4000 - # 7FFF always located page 5, and at # 8000 - # BFFF is always page 2. Usually assembled on a chip KP11 (DD2). 4) the address selector # C000-# FFFF. When referring to these addresses the processor switches the multiplexer to the map at # C000-# FFFF is not page 1 (as in sorokvosmyh machines), and page numbers included in the system registry. Assembled on a single logical element AND-NOT (IC LA3, DD4.1). 5) control scheme rulers of RAM. Includes only one line of RU5, excluding choice of different data from one address. Otherwise upon application to the same address are issued Data from the zero line of chips from the first time. Second prednazachenie this scheme - the inclusion of the zero line at memory access TV-shaper. Need to display, located as Once the zero line. Collected in shallow logic (DD5.1-3, DD4.2). 6) Block diagram of recording a zero address. Because after power on and after RESET is set zero memory bank, the record at # 0000 - # 3FFF is like writing on # C000-# FFFF. Usually port of the first five cells in a zero bank, result, do not go for some programs. The scheme collected in shallow logic (DD5.4). In the 128th car to be more musical co-processor, but are not given a diagram of its connection, since considered only increase the amount of memory. All of the above may seem frightening and confusing, but it is really only 4-5 buildings of chips and two dozen wires. Because nowhere information was available to expand memory Synthesis, then I will tell you how to get around some of the "breakup" with its expansion. In principle, used altered scheme of Revue 94 / 4, but the signals DOS Active and ROM Enable collect is not necessary, because they already have in the synthesis of (signals and BJ-BROM-, respectively). All other signals suitable for Synthesis. Be sure to think you really can build and develop the scheme, or is it better to Komel? Now on "Oblomov" that might arise from those who himself has expanded memory. First: the signal H1 in Leningrad and the synthesis of different amplitude, so you must use S1. The second and largest: a synthesis of signals A14 and A15 form a single signal MA7. For 48k is not terrible, but here in the 128k is the intersection of addresses and a few memory cells are not available. Exit: to to change the A14 (which selects the row RAS for MA7) and A13 (which selects the column CAS to MA6), plus swaps sotvetstvuyuschie signals videoformirovatelya (third and 4th leg DD26). Ie cuts a path from most pins and connect the wires with new legs. That is, in principle, and all. _______________________________________End

Other articles:

Similar articles:

В этот день... 30 March