ЭЛЕКТРИЧЕСКИЕ СХЕМЫ УЗЛОВ ЗАПИСИ

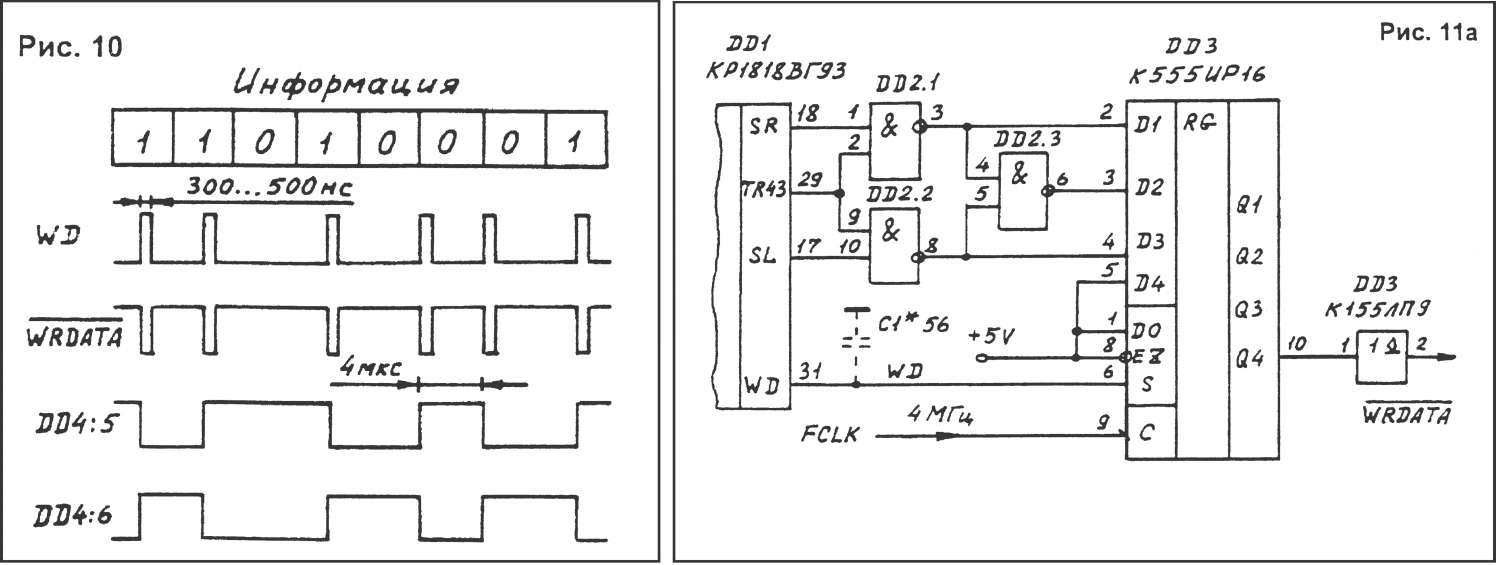

Если сравнить между собой вре-

менные параметры сигналов WD

и -WRDATA, можно понять, почему,

вопреки рекомендациям разработчи-

ков [6], работает схема простейшего

узла записи, приведенная на рис.9

(CPU "Балтик", "Эрик").

Выходной сигнал контроллера -

WRDATA получается путем логичес-

кого инвертирования сигнала WD.

Это возможно, т.к. допуски на дли-

тельность WRDATA больше, чем на

WD. Далее -WRDATA через разъем

X1 по кабелю поступает в дисковод.

Для примера выбран отечественный

НГМД МС5305.

печивает деление на 2 входной час-

тоты (рис. 10).

Это понятно, т.к. цифровую ин-

формацию несет не длительность -

WRDATA, а его период.

С парафазных выходов триггера

сигнал записи поступает через диод-

но-резистивный коммутатор на маг-

нитную головку (МГ).

Небольшая тонкость. Запись про-

исходит благодаря перепадам тока

в МГ. Ширина элементарного маг-

нитного "отпечатка" определяется в

первую очередь конструкцией МГ и

параметрами ферроматериала дис-

кеты.

Как видно, длительность сигнала

-WRDATA принципиального значе-

ювелирной юстировке дисковода,

фирменной сборке, высоком качест-

ве дискет — и с внутренних дорожек.

Возможность обмена записями с

коллегами всетаки остается пробле-

матичной, т.к. при смене дисковода

уверенное чтение информации с

последних дорожек не гарантирует-

ся из-за эффекта "сдвига пиков".

(Продолжение. Начало в NN10-11/98)

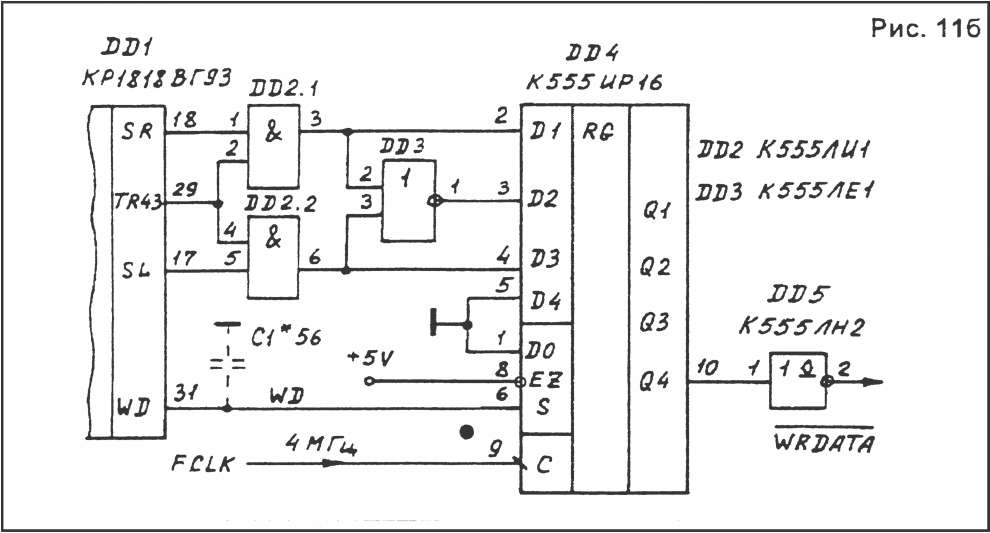

Разработчики быстро оценили

недостатки простейшей схемы и пе-

решли к более сложным (рис. 11а —

CPU "ОРИОН-128", рис.11б — CPU

"ATM-TURBO-2").

Во-первых, в этих схемах длитель-

ность импульса выходного сигнала

-WRDATA стала меньше по сравне-

нию с исходным WD практически в 2

раза — 250 нс вместо 300...500 нс.

Суть нововведения не столько в са-

мой величине длительности, сколько

в принудительной фазировке и пе-

реднего, и заднего фронтов сигнала.

Во-вторых, для уменьшения фа-

зовых искажений вводится предком-

пенсация сигналов -WRDATA при

записи начиная с сорок четвертой

дорожки и далее.

При неустойчивой работе регист-

ра в подобных схемах иногда вводят

конденсатор С1* (показан пункти-

ром), который сдвигает во времени

импульсные последовательности на

входах S и С. Другое решение — ин-

версия сигнала FCLK.

Поясняющие временные диа-

граммы приведены на рис.12.

Логика функционирования обеих

схем идентична. Разница заключа-

Нагрузкой инвертора с открытым

коллектором DD2 является низкоом-

ный резистор R1. Инвертор DD3 уве-

личивает крутизну фронта сигнала,

подаваемого на синхровход триггера

DD4.

При высоком уровне сигнала

"Разрешение записи" триггер обес-

ния не имеет, важно, чтобы расстоя-

ние между передними фронтами им-

пульсов было жестко сфазировано и

не "плавало".

Информация, записанная при

помощи приведенной схемы, как

правило, без вопросов считывается

с внешних дорожек дискеты, а при

ется в инверсии некоторых внутрис-

хемных сигналов, что не имеет боль-

шого значения.

Принцип работы узла защиты за-

ключается в том, что по переднему

фронту сигнала WD в сдвиговый ре-

гистр К555ИР16 заносится код, опре-

деляемый логическими уровнями на

40...43-й дорожек для некоторых ти-

пов дисководов.

К нюансам схемы относится при-

менение не совсем чистого меандра

FCLK 4 МГц, который поступает со

схемы цифрового выделения дан-

ных узла чтения. Такое решение уп-

рощает общую схему контроллера,

но не ухудшает параметры, так как в

режиме записи этот сигнал все рав-

но остается строгим меандром.

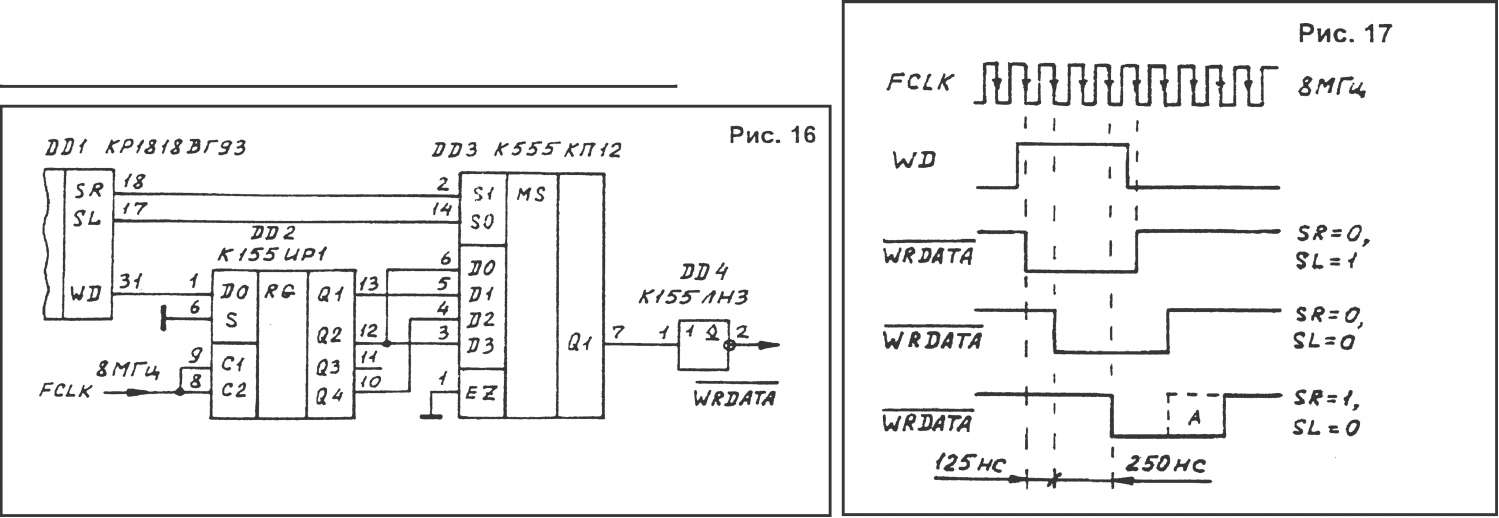

Дальнейшее развитие темы пред-

ложено в схеме рис. 16, временные

диаграммы работы которой пред-

ставлены на рис. 17 (усовершенс-

твованный контроллер для CPU

"ВЕКТ0Р-06Ц").

Сдвиговый регистр выполнен на

микросхеме К155ИР1. Важной осо-

бенностью схемы является увеличе-

ние тактовой частоты FCLK с 4 МГц

до 8 МГц. За счет этого появляется

возможность установить задержку

предкомпенсации равной 125 нс, что

вдвое меньше по сравнению с пре-

дыдущими схемами.

Имеется еще одна особенность

схемы, очень привлекательная с точ-

ки зрения практики. Связка "регистр

К155ИР1 - мультиплексор К555КП12"

позволяет установкой перемычек

изменять время предкомпенсации

в довольно широких пределах отде-

входах Dl...D4. По окончании сигнала

WD этот код выводится из регистра в

последовательном виде через выход

11 к выводу 10 микросхемы DD3 (по-

казано пунктиром).

Еще одна разновид-

ность схем с применени-

ем регистра К555ИР16

изображена на рис.15

(CPU "KAY-256").

Отличительная осо-

бенность схемы — от-

сутствие сигнала TR43,

то есть предкомпенса-

ция производится для

всех без исключения

дорожек — как внешних,

так и внутренних.

Q4 синхроимпульсами FCLK (4 МГц).

Период повторения синхроимпуль-

сов FCLK составляет 250 нс, что и

определяет длительность выходного

сигнала -WRDATA.

В зависимости от комбинации

сигналов SR, SL, TR43, на выходе

формируют импульсы одинаковой

длительности, сдвинутые друг отно-

сительно друга на 250 нс. Компенса-

ция фазовых искажений происходит

автоматически — ВГ93 сам "знает",

когда выдавать сигналы SR и SL.

На рис.13 показан случай, когда в

некоторых контроллерах сигнал сни-

мается не с выхода Q4, а с выхода

Q3 регистра. К чему это приводит?

Для записи без предкомпенсации

(SR=0, SL=0) и для записи с отста-

ванием (сдвиг вправо) (SR=1, SL=0)

форма импульсов остается прежней.

Однако для записи с опережением

(сдвиг влево) (SR=0, SL=l) длитель-

ность импульса -WRDATA расши-

ряется и становится равной 500 нс

(рис. 14).

Нельзя признать это логичным и

оправданным, поскольку тем самым

вводится непропорционально боль-

шое значение сдвига влево. Схему

рис.13 легко привести к стандартно-

му виду перепайкой цепи от вывода

Логика простая — на внешних до-

рожках условия для считывания хо-

рошие, и некоторая "перекомпенса-

ция" не ухудшает параметры чтения,

так как расстояние между участками

с разной намагниченностью (рис.6)

достаточно велико. Напротив, при

приближении к дорожке с номером

43 в данном случае происходит

плавное наращивание задержек от-

ставания/опережения. Следователь-

но, исчезают проблемы с неустойчи-

вым чтением информации в районе

льно для сдвига вправо и отдельно

для сдвига влево. Таким образом,

можно оптимально учесть особен-

ности конкретного типа дисковода.

Как известно, величина "сдвига

пиков" при записи зависит от массы

факторов и однозначному расчету не

поддается. Ее определяют опытным

путем. Например, по мнению авторов

схемы, изображенной на рис.16,для

японских 80-дорожечных дисково-

дов ТЕАС (FD-55) лучше подходят

задержки: опережения - 125 нс и от-

ставания - 250 нс.

Данный факт не

противоречит теории

[7], согласно которой

реальные отклики маг-

нитных "отпечатков"

имеют асимметричную

форму вследствие

эффекта саморазмаг-

ничивания и нелиней-

ности перехода намаг-

ниченности носителя.

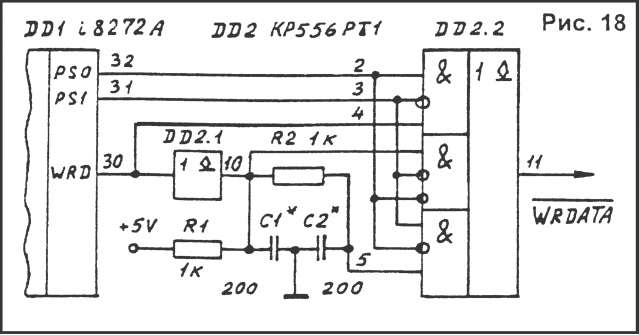

Подбор задержки

предкомпенсациипред-

лагают и разработчики

универсальной платы

контроллера #МС5301

(рис.18), выполненной

на базе i8272A [10].

Конденсаторами С1* и

С2* устанавливают за-

держки соответственно

опережения и отста-

вания. Все логичес-

кие связи выполнены

внутри программируе-

мой матрицы DD2, что

позволяет максималь-

но упростить конструкцию. Особен-

ность схемы - отсутствие жесткой

фазировки выходных сигналов изза

RC - формирователей.

При этом период сигнала -

WRDATA в большей степени подвер-

жен изменению вследствие темпера-

турных колебаний, нестабильности

питающего напряжения и наводок.

(Продолжение следует)