МИКРОПРОЦЕССОР Z80

СИСТЕМА КОМАНД

Помимо 78 команд своего предшественника — микропроцессора

18080, в Z80 реализовано 80 новых. В целом он обрабатывает 696 кодов

операций (с учетом использования в командах различных регистров,

способов адресации и т. п.).

Для каждой команды приведено мнемоническое обозначение на

языке ассемблера, схема, поясняющая ее работу, и состояние флагового

регистра после выполнения команды.

При записи команд приняты следующие обозначения:

А — 8-разрядный регистр аккумулятора;

В, С, D, Е, Hf L — 8-разрядные регистры данных;

I — 8-разрядный регистр вектора прерываний;

R — 8-разрядный регистр регенерации динамического ОЗУ;

AF — 16-разрядный регистр, старший байт которого содержит значение

аккумулятора, а младший байт — значение флагового регистра;

BCf Dc, HL — 16-разрядные спаренные регистры;

IX, IV — 16-разрядные индексные регистры;

SP — 16-разрядный регистр указателя стека;

PC — 16-разрядный регистр счетчика команд;

п — 8-разрядный операнд, непосредственно указанный в команде;

nn — 16-разря/шый операнд, непосредственно указанный в команде;

(HL), (ВС), (DE) — 8-разрядные значения ячеек памяти, адреса которых

содержатся в соответствующих регистровых парах;

(nn) — в командах, оперирующих байтами:

8-разрядное значение ячейки памяти, адрес которой задается двумя

бантами nn непосредственно в команде;

(nn) — в командах, оперирующих 16-разрядными значениями:

16-разрядное значение смежных ячеек памяти, адрес nn первой из кото-

рых (младшего байта значения) указан непосредственно в команде,

адрес второй ячейки (старшего байта значения) равен пп+1;

(IX+a), (IY+d) — 8-разрядные значения ячеек памяти, адреса которых

вычисляются сложением значения соответствующего индексного ре-

гистра и 8-разрядного смещения d, указанного непосредственно в

команде;

Ь — номер участвующего в операции бита (0...7);

сс — условие, при истинности которого выполняется команда;

е — 8-разрядное смещение относительно текущего адреса;

CY — значение фл&а переноса;

{ — состояние флага изменяется в результате операции;

• — состояние флага не изменяется в результате операции;

0 — флаг сбрасывается в результате операции;

1 — флаг устанавливается в результате операции;

X — состояние флага не определено;

V — флаг P/V индицирует арифметическое переполнение в результате

операции;

Р — флаг P/V индицирует «четность» в результате операции.

Операнд, из которого берется значение для выполнения опера-

ции, называется источником, а операнд, в который помещается резуль-

тат — приемником. В мнемониках команд, использующих два операнда,

первым, как правило, записывается приемник, затем, через запятую, —

источник. В процессе выполнения команды содержимое источника не

меняется. Если команда содержит один операнд, то он одновременно

может быть и источником, и приемником.

МЕТОДЫ АДРЕСАЦИИ

После описания каждого метода адресации приведено по два примера

его использования.

Безоперандные команды. Для их выполнения процессору не требуется

дополнительных значений:

HALT

NOP

Регистровая адресация. Операнд содержится в регистре, который

непосредственно указан в команде:

INC А

ADD HL.BC

Непосредственная адресация. Операнд расположен в ячейке памяти,

непосредственно следующей за кодом команды. Если операнд двухбайтовый,

то он занимает две ячейки за кодом команды (расширенная непосредствен-

ная адресация):

LD С,%1011

LD HL,#1234

Неявная адресация. Регистр, в котором содержится операнд, однознач-

но определен данной командой:

RLA

LDIR

Регистровая косвенная адресация. Операнд расположен в ячейке

памяти, адрес которой содержится в регистровой паре:

DEC (HL)

LD А,(ВС)

Далее по тексту для обозначения этого типа адресации будет исполь-

зоваться фраза: «операнд расположен в ячейке, адресуемой регистром».

Индексная адресация. Адрес размещения в памяти операнда образу-

ется сложением значения индексного регистра и некоторого смещения

(—128...+127), явно указанного в команде:

SLA (IX+2)

LD A,(IY-25)

Косвенная адресация. Адрес операнда содержится в ячейках памяти,

расположенных непосредственно за кодом команды:

LD А, (1234)

LD (#C000),DE

Побитовая адресация. Командой задается конкретный бит операнда,

над которым будет проводиться операция:

SET 4f(HL)

BIT 7. А

Относительная адресация* Адрес задается как однобайтовое смещение

(—128...+127) относительно текущего значения регистра счетчика команд*:

1R $+#23

DJNZ $-6

Расширенная адресация. Адрес задается двухбайтовым операндом:

CALL 1234

JP NC,#1601

Различные методы адресации могут быть совмещены в командах,

работающих с двумя операндами:

LD (HL),12

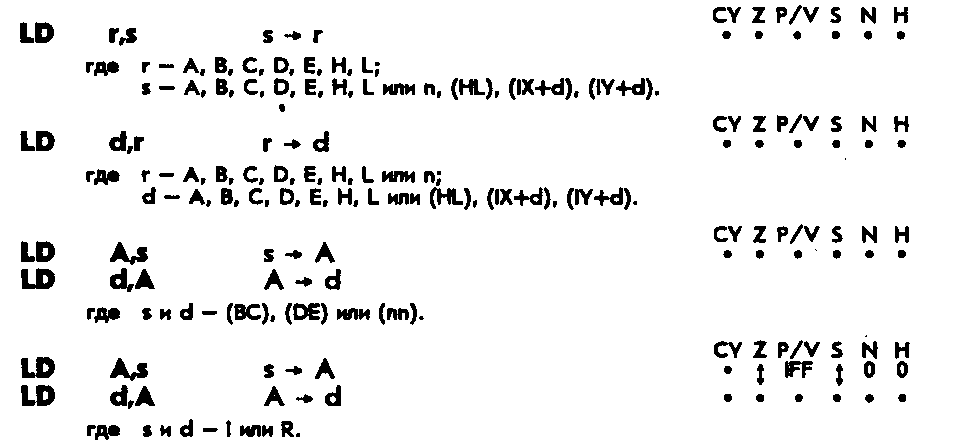

Команды пересылок

Пересылка байта из йсточиика в приемник без изменений. Содержимое

флагового регистра F не меняется. Исключение составляют команды

Пересылка байта из йсточиика в приемник без изменений. Содержимое

флагового регистра F не меняется. Исключение составляют команды

*) Необходимо учитывать, что код смещения, содержащийся в коде команды

и записанный в тексте ассемблера, будет различным. Ассемблер отсчи-

тывает смещения относительно счетчика адресов $, хранящего адрес

команды, тогда как микропроцессор использует содержимое регистра РС,

увеличивающееся каждый раз при выборе очередного байта команды из

памяти.

LD А,1 и LD A,R, которые отображают состояние триггера разрешения

прерываний в бите четности/переполнения P/V регистра флагов.

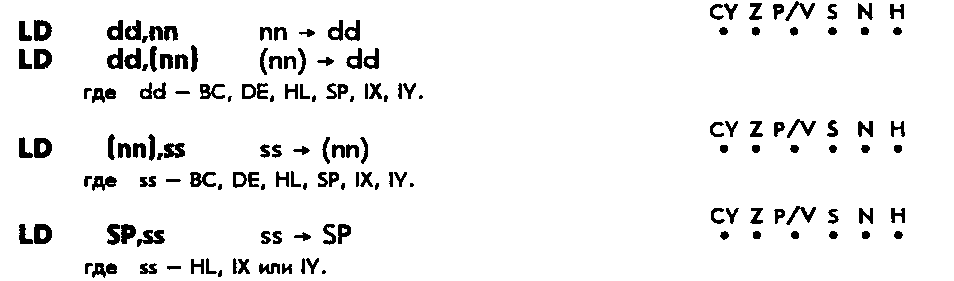

Пересылка двух байтов из источника в приемник без изменении.

Пересылка двух байтов из источника в приемник без изменении.

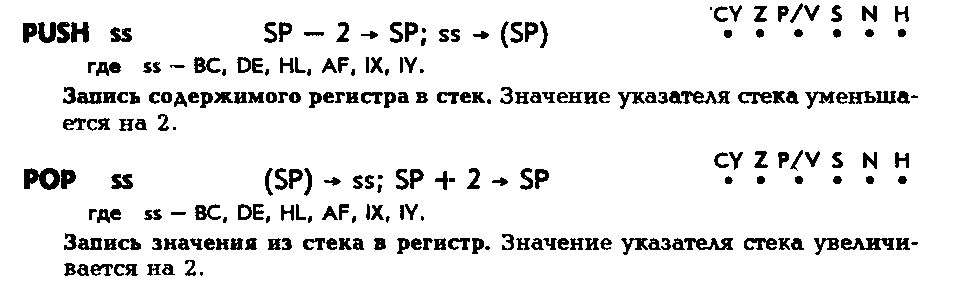

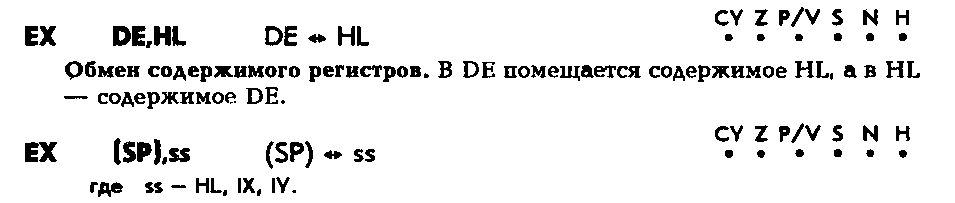

Команды информационного обмена

Обмен со стеком. Значение вершины стека меняется местами с содержи-

мым регистра ss (значение указателя стека не изменяется).

Обмен со стеком. Значение вершины стека меняется местами с содержи-

мым регистра ss (значение указателя стека не изменяется).

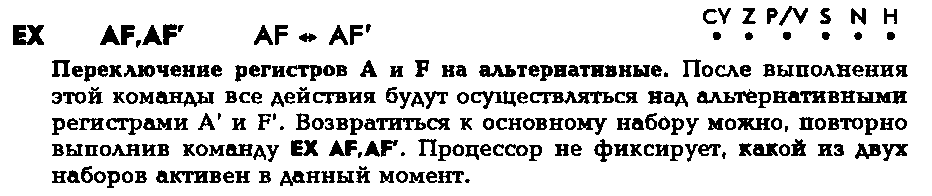

Команды переключения набора регистров

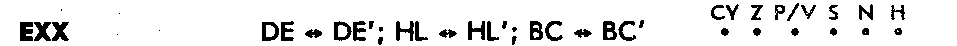

Переключения активного набора регистров. Если ранее активным являлся

основной набор (HL, DE, ВС), то после выполнения команды — альтерна-

тивный (HL DE', ВС'), и наоборот. Команда аналогична команде EX AF,AFr.

Команды пересылки блока и команды поиска

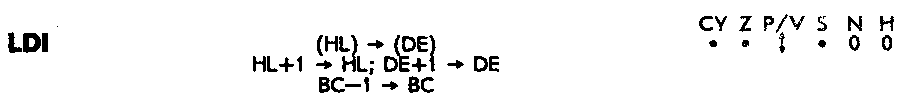

Пересылка содержимого ячейки памяти с инкрементом. Байт из ячейки,

адресуемой регистром HL, пересылается в ячейку, адресуемую регистром

DE, содержимое регистров НЬи DE увеличивается на единицу, а регистра

ВС уменьшается на единицу. Если в результате выполнения команды

ВС=0, то флаг P/V сбрасывается, в противном случае P/V-1.

Пересылка содержимого ячейки памяти с инкрементом. Байт из ячейки,

адресуемой регистром HL, пересылается в ячейку, адресуемую регистром

DE, содержимое регистров НЬи DE увеличивается на единицу, а регистра

ВС уменьшается на единицу. Если в результате выполнения команды

ВС=0, то флаг P/V сбрасывается, в противном случае P/V-1.

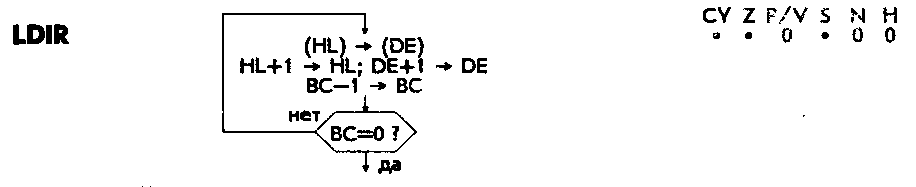

Пересылка блока памяти с инкрементом. Действие аналогично команде

LDI, только пересылается группа байт, расположенных в сторону увели-

чения адресов от ячейки, адресуемой регистром HL. Количество переда-

ваемых байт определяется регистром ВС. Аналогичного результата можно

добиться, выполнив фрагмент программы:

Пересылка блока памяти с инкрементом. Действие аналогично команде

LDI, только пересылается группа байт, расположенных в сторону увели-

чения адресов от ячейки, адресуемой регистром HL. Количество переда-

ваемых байт определяется регистром ВС. Аналогичного результата можно

добиться, выполнив фрагмент программы:

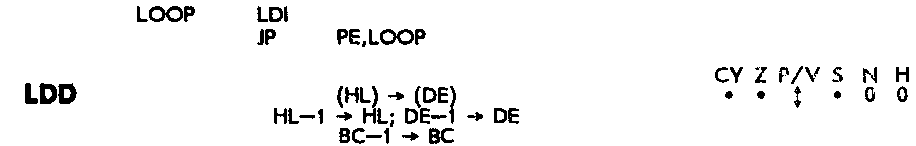

Пересылка содержимого ячейки памяти с декрементом. Байт из ячейки,

адресуемой регистром HL, пересылается в ячейку, адресуемую регистром

DE, содержимое регистров HL, DE и ВС уменьшается на единицу. Если

в результате выполнения команды ВС=0, то флаг P/V сбрасывается, в

противном случае P/V=l.

Пересылка содержимого ячейки памяти с декрементом. Байт из ячейки,

адресуемой регистром HL, пересылается в ячейку, адресуемую регистром

DE, содержимое регистров HL, DE и ВС уменьшается на единицу. Если

в результате выполнения команды ВС=0, то флаг P/V сбрасывается, в

противном случае P/V=l.

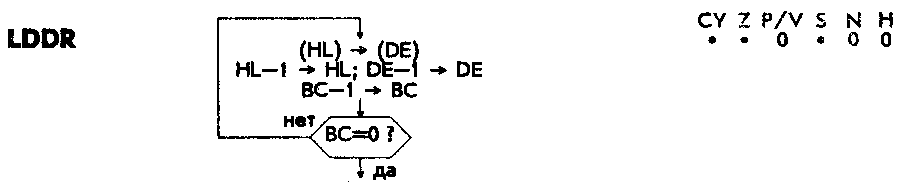

Пересылка блока памяти с декрементом. Действие аналогично команде

LDOi только пересылается группа байт, расположенных в сторону умень-

шения адресов от ячейки, адресуемой регистром HL. Количество переда-

ваемых байт определяется регистром ВС, Аналогичного результата можно

добиться, выполнив фрагмент программы:

LOOP LDD

JP PE.LOOP

JP PE.LOOP

Сравнение значения аккумулятора с содержимым ячейки памяти с

инкрементом. Ячейка памяти адресуется HL. Если A=(HL), устанавлива-

ется флаг Z, в противном случае Z=Q. После сравнения содержимое

регистра HL увеличивается на единицу, а ВС на единицу уменьшается.

Если в результате выполнения команды ВС=0, то флаг P/V сбрасывается,

в противном случае P/V— 1.

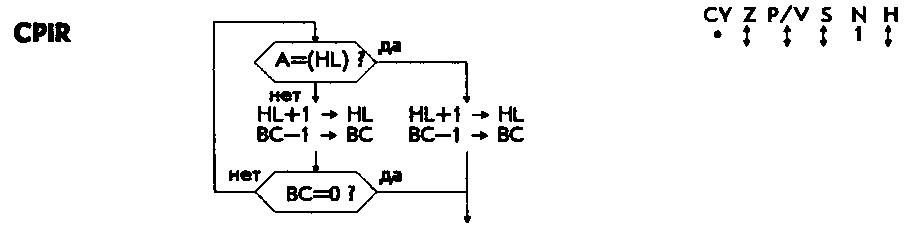

Поиск значения аккумулятора в блоке памяти с инкрементом. Начальный

адрес блока задается регистром HL, длина — регистром ВС. Поиск

производится в сторону увеличения адресов. При совпадении значения

аккумулятора с содержимым ячейки памяти устанавливается флаг Z

(если байт не найден — Z=0), регистр HL будет содержать адрес последу-

ющей ячейки в блоке, а ВС — ее обратный порядковый номер.

Сравнение значения аккумулятора с содержимым ячейки памяти с декре-

ментом. Ячейка памяти адресуется регистром HL. Если A=(HL), устанавли-

вается флаг Z, в противном случае Z=0. После сравнения значения реги-

стров HL и ВС уменьшаются на единицу. Если в результате выполнения

команды ВС=0, то флаг P/V сбрасывается, в противном случае P/V=l.

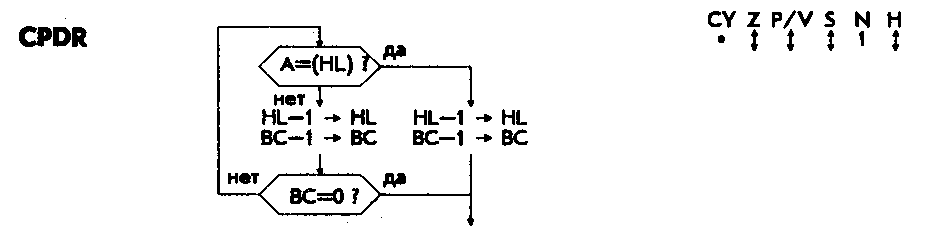

Сравнение значения аккумулятора с содержимым ячейки памяти с декре-

ментом. Ячейка памяти адресуется регистром HL. Если A=(HL), устанавли-

вается флаг Z, в противном случае Z=0. После сравнения значения реги-

стров HL и ВС уменьшаются на единицу. Если в результате выполнения

команды ВС=0, то флаг P/V сбрасывается, в противном случае P/V=l.

Поиск значения аккумулятора в блоке памяти с декрементом. Конечный

адрес блока задается в регистре HL, длина — в регистре ВС. Поиск

производится в сторону уменьшения а/фесов. При совпадении значения

аккумулятора с содержимым ячейки памяти устанавливается флаг Z

(если байт не найден — Z=0), регистр HL будет содержать адрес предыду-

щей ячейки в блоке, а ВС — ее порядковый номер.