АРХИТЕКТУРА ZX SPECTRUM 128

Внутреннее строение ZX Spectrum 128, с точки зрения программиста,

не сильно отличается от обычного Speccy. Из основных отличий следует

отметить увеличение вдвое объема постоянной памяти: оперативная память,

как следует из названия, увеличилась до 128К. Кроме этого, в состав

компьютера был добавлен новый узел — музыкальный процессор.

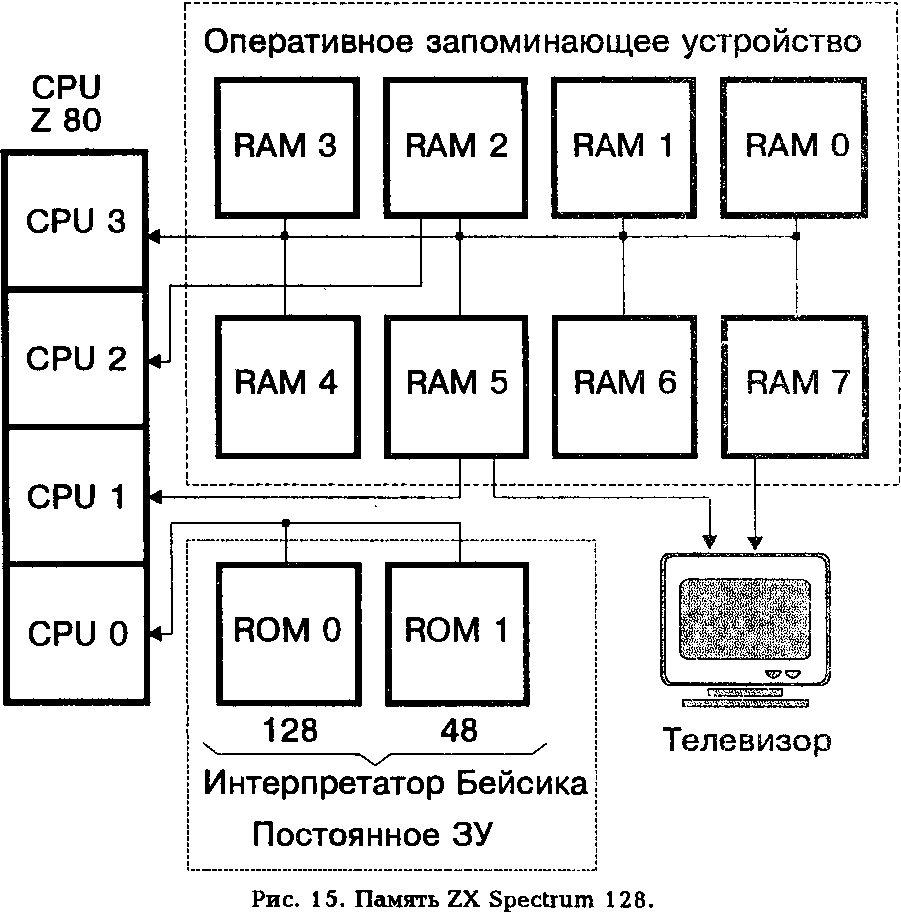

Как следует из сказанного выше, общий объем памяти в 128 модели

достиг 160К, процессор же непосредственно может адресовать только 64К

из них. Выход из этого положения был найден сравнительно легко — через

механизм страничной адресации памяти. Адресное пространство процессора

было разделено на четыре равных раздела по 16К (иногда их называют

окнами), мы будем обозначать их CPU0...CPU3. Раздел CPU0 занимает адреса

0...#3FFF, CPU1 — #4000...#7FFF, CPU2 — #8000...#BFFF и CPU3 —

#C000...#FFFF. Вся память также была разделена на сегменты по 16К,

называемые еще банками памяти, или страницами памяти. Мы будем обоз-

начать банки ПЗУ через ROMO и ROM1, а банки ОЗУ от RAM0 до RAM7.

Через специальный механизм (который мы рассмотрим ниже) программист

может по своему усмотрению устанавливать в адресные разделы микропро-

цессора те или иные банки памяти. На рис. 15 показано, какая память где

может находиться.

Банк ROMO содержит расширение интерпретатора языка Бейсик,

встроенного в компьютер, написанное специально для 128 модели, а содер-

жимое ROM1 практически полностью совпадает с ПЗУ из стандартного ZX

Spectrum. Находиться эти банки могут только в адресном разделе микропро-

цессора CPU0. Разделам CPU1 и CPU2 соответствуют фиксированные банки

ОЗУ, RAM2 и RAM5 соответственно. В разделе CPU3 можно установить

любой из банков ОЗУ.

Наличие большого количества оперативной памяти позволило не-

сколько расширить возможности отображения информации: в

ZX Spectrum 128 есть две экранные области памяти (так называемые видео-

страницы). Одна — стандартая, такая же, как и в обычном Speccy. Она

расположена в адресах #4000...#5AFF, следовательно, в банке памяти

RAM5. Вторая находится в начале банка оперативной памяти RAM7. Обра-

титься к этой памяти можно только тогда, когда этот банк установлен в

разделе CPU3 микропроцессора. Строение экрана при этом осталось неиз-

менным, таким образом, все элементы экрана оказываются расположенны-

ми в адресном пространстве #C000...#DAFF.

Распределение памяти при работе из Бейсика следующее. Адресному

разделу процессора CPU0 соответствует банк ПЗУ ROM1, разделу CPU3 —

банк ОЗУ RAM7. Как уже говорилось, содержимое разделов CPU! и CPU2

фиксировано. Именно такой конфигурация памяти будет при загрузке

программ с магнитофона или при выполнении функции USR. Заметим, что

организация памяти при работе интерпретатора Бейсика практически не

отличается от таковой в обычном ZX Spectrum. Исключение составляет

только область буфера принтера, где Бейсик располагает ряд новых систем-

ных переменных. А принтер стал более «честным», теперь к компьютеру

можно подключить практически любой принтер, имеющий стандартный

последовательный интерфейс RS-232 и систему команд, совместимую с

EPSON.

Объем и направленность книги не позволяют детально остановиться

на новшествах во встроенном программном обеспечении ZX Spectrum 128.

Скажем только, что интерпретатор Бейсика практически остался старым,

добавлены только два новых оператора: для управления музыкальным про-

цессором и для перехода в режим эмуляции обычного Speccy. Кроме этого

расширено использование некоторых «старых» операторов, использующих-

ся для управления принтером и для работы с так называемым «электронным

диском»*.

Механизм страничной адресации памяти, а также музыкальный про-

цессор и иная организация принтера потребовал расширения стандартных

внешних устройств, обрабатываемых «внутри» компьютера. Выше писалось,

что выбор устройств в ZX Spectrum осуществляется сбросом в ноль какого-

либо разряда шины адреса. Для ZX Spectrum 128 это верно только наполо-

вину. Действительно, для обращения к дополнительным портам в младших

восьми разрядах устанавливается в ноль адрес А1. Таким образом, общий

адрес внешних устройств должен быть #FD. Выбор же конкретного устрой-

ства определяют адреса А14 и А15.

Порт 32765 l#7FFD, %1111111111111101)

Отдельными битами этого порта осуществляется управление конфи-

гурацией компьютера. Отметим, что этот порт доступен только для записи,

поэтому интерпретатор Бейсика в системных переменных по адресу 23388

(#5В5С) хранит копию этого регистра:

биты 0...2 определеяют номер страницы ОЗУ, установленной в адресном

разделе CPU3 микропроцессора:

000 (0) - RAM0

001 (1) - RAMI

010 (2) - RAM2

011 (3) - RAM3

100 (4) - RAM4

101 (5) - RAM5

110 (6) - RAM6

111 (7) - RAM7

бит 3 управляет режимом отображения информации, точнее, номером

видеостраницы, содержимое которой выводигся на монитор. Если бит

сброшен, то на дисплей выводятся значения из стандартной экранной

области памяти, расположенной в адресах #4000...#5AFF (банк

RAM5). Если же бит установлен, то отображаются данные из второй

видеостраницы, находящейся в банке RAM7. Обратите внимание, что

такое решение позволяет полностью исключить «видеопамять» из

адресного пространства микропроцессора и подключать ее по мере

необходимости, тогда как изображение на экране будет выводиться

постоянно;

бит 4 определяет содержимое адресного раздела микропроцессора CPU0.

Если бит сброшен, то адресуется банк ROMO, содержащий коды

расширения интерпретатора Бейсика; если бит установлен, в адресах

*) Более подробно об этом можно прочитать в книге «Диалекты Бейсика для

ZX Spectrum».

0...#3FFF будет находиться банк ROM1, где хранится практически не

измененная копия обычного ПЗУ Speccy.

бит 5 управляет режимом совместимости с обычным ZX Spectrum, уста-

новка этого бита приведет к отключению дополнительной памяти,

таким образом, компьютер практически полностью превратится в

старый добрый Speccy. Отметим, что сбросить значение этого бита

программным путем невозможно, необходим аппаратный «сброс»

всего компьютера.

Остальные биты из этого порта не используются.

Порт 49149 (#BFFD, %1011111111111101)

Порт 65533 (#FFFD, %1111111111111101)

Через эти порты осуществляется адресация восьмиразрядных регист-

ров музыкального процессора. Всего таких регистров шестнадцать, мы будем

обозначать их R0...R15. Регистры двунаправленные, то есть информацию в

них можно записывать и считывать. Для доступа к какому-либо регистру его

номер (число в диапазоне от 0 до 15) необходимо записать по адресу 65533.

После этого становится возможна передача данных между этим «установлен-

ным» или текущим регистром и микропроцессором. Для смены текущего

регистра соответствующий номер нужно записать в порт 65533, и так далее.

Обратите внимание, что адреса для чтения и записи информации в

текущий регистр музыкального процессора различны. Для записи байта

нужно выполнить команду вывода в порт с адресом 49149, а для чтения —

команду ввода из порта с адресом 65533.

Прежде чем разобрать функции отдельных регистров музыкального

процессора, остановимся на его особенностях. Микросхема музыкального

процессора имеет три независимых канала для формирования звука (обоз-

начаются А, В и С) и два двунапрвленных восьмиразрядных канала вво-

да/вывода — IRA и IRB, соответственно. Через канал IRA осуществляется

связь с принтером, вывод сигналов для специального музыкального интер-

фейса MIDI и, кроме этого, связь со специальной выносной клавиатурой

функциональных клавиш, используемых в расширенном интерпретаторе

Бейсика.

__Регистры RO/RI, R2/R3, R4/R5

Три спаренных регистра R0/R1, R2/R3, R4/R5 используются для вы-

работки частоты тона соответственно каналов А, В и С. Необходимые двенад-

цатиразрядные значения образуются из восьми бит младшего по номеру

регистра и четырех младших бит старшего по номеру регистра.

Регистр R6

Младшие пять разрядов этого регистра задают частоту шума.

Регистр R7

Через этот регистр осуществляется управление звуковыми каналами

и регистрами ввода/вывода:

биты 0...2 используются для управления выводом частоты тона. Установка

битов 0, 1 или 2 приведет к запрещению вывода частоты тона в

каналы А, В и С соответственно;

биты 3...5 используются для управления выводом частоты шума. Установ-

ка битов 3, 4 или 5 приведет к запрещению вывода частоты шума в

каналы А, В и С соответственно;

биты в и 7 устанавливают режим работы каналов IRB и IRA соответст-

венно. При сброшенном бите канал работает на ввод, а при установ-

ленном — на вывод информации.

Регистры R8, R9 и RfQ

Младшие пять разрядов регистров R8, R9 и R10 управляют соответст-

венно амплитудой каналов А, В и С.

Регистры R11/R12

Спаренные регистры RH/R12 образуют шестнадцатиразрядное зна-

чение огибающей выходного сигнала, регистр R11 несет младший байт, а

R12 — старший.

Регистр R13

Младшие четыре разряда этого регистра управляют формой и режи-

мом огибающей выходного сигнала:

бит 0 — затухание;

бит 1 — чередование;

бит 2 — нарастание;

бит 3 — продолжение.

Регистры R14 и R15

Регистры R14 и R15 используются соответственно для связи с канала-

ми ввода/вывода IRA и IRB. Содержимое этих регистров можно в любой

момент считывать и записывать, на формировании звука это никак не

отражается.