|

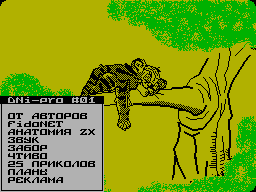

Dni-Pro #01

18 ноября 2000 |

|

Iron - LSI architecture parallel KP580BB55.

LSI PARALLEL ARCHITECTURE

INTERFACE KP580BB55.

PART I

LSI programmable parallel interface (PPI) KP580BB55 is

designed to provide input / output parallel data in various

formats and allows you to implement most of the known protocols

exchange on the parallel channels. (PPI) can be used for

conjugation microprocessor with standard peripheral equipment

(display, teletype, storage), etc. The block diagram of PPI is

shown in Figure 1 The composition of BIS include:

bi-directional 8-bit data buffer (BD), binds PIP with the

system bus data controller read / write (RWCU), which provides

Figure 1> PORT PA (7-0)

CUA <<> A <>

<

D (7-0)

<> BD <>

> PORT PC (7-4)

<> C <>

RD <

>

WR

> PORT PC (3-0)

A1 RWCU <> C <>

>> <

A0 √

>

RESET PORT PC (7-0)

> CUB <<> B <>

> <

CS ^

Ucc>

GND>

management of external and internal data transfer, control

words and information about the state of TTR, three 8-bit

channel input / output (PORT A, B and C) for the exchange of

information with external devices; scheme

Control group A (CUA), which generates

upravieniya signals of channels A and senior

bits of the channel C [PC (7-4)]; control circuit group B

(CUB), which generates signals control channel B and the LSB

channel C [PC (3-0)].

Purpose input, output and control signals are given when

describing the PPI pins in Table 1. Pairing BIS KP580BB55 with

a standard system bus shown in Figure 2. Signals control the

operation of PPI are fed to block RWCU (Fig. 1) and along with

the address inputs A0, A1 ask type of operation carried out by

BIS (Table 2).

Tablittsa 1. Description findings PPI

denotes the number of the destination

s O contact O

D (7-0) 27, 28, 29 input / output data

30, 31, 32

33, 1934

RD 5 Reading; L-level system

drove authorizes assume

tyvanie information

from the register at

emogo on inputs A0,

A1 on the bus D (7-0)

WR 36 Writing; L-level system

drove allows listings

is information with a wide

Ny D (7-0) in the register

PPI, addressable by

inputs A0, A1

A0, A1; 9 8 inputs for addressing

internal registers

PPI

RESET 1935 Reset; H-level signal

signal resets Regis

spectrum manager cl

Peninsula and sets

all ports in the regime

I

CS Chip Select 6; L

-Level signal

dklyuchaet PPI to the system

emnoy bus

PA (7-0) 37, 38, 39, Input / Output channel A

40, 1, 2, 3

4

PB (7-0) 15, 24, 23 Input / Output channel B

22, 21, 20

19, 1918

PC (7-0) 10, 11, 12 input / output channel C

13, 17, 16

15, 1914

Ucc 26 Power (+5 V)

GND 7 Power (0 V)

Figure 2

AB

CB

DB

^

√ √ √ √ √ √ √

A0 A1 CS D (7-0) RD WR RESET

KP580BB55

PA (7-0) PC (7-4) PC (3-0) PB (7-0)

^ ^ ^ ^

√ √ √ √

Tablittsa 2. Operations, asked Governors

sponding signals of TTR

Control Signals

OPERATION

CS RD WR A1 A0

Record control 0 1 0 1 1

word of the MP

Write to channel A 0 1 0 0 0

>>>>>> B 0 1 0 0 1

>>>>>> C 0 1 0 1 0

Reading from a channel A 0 0 1 0 0

>>>>>> B 0 0 1 0 1

>>>>>> C 0 0 1 1 0

Disabling the PPI from 1 XXXX

D (7-0)

Note. X - do not care condition

signal

Mode of each channel PPI programiruetsya using the control

word. Control word can specify one of three modes: main mode of

I / O (Mode 0), gated I / O (mode 1)

bidirectional transmission

(Mode 2). One control word can be

set different modes for each channel. Control word format is

shown in Figure 3.

Fig.3

D D D D D D D D

7 6 5 4 3 2 1 0

Rezhim0 0 0

Group mode1 0 1 1 Input

A rezhim2 1 0 PC (3-0)

0 Output

Input 1

PA (7-0) 1 Input

Conclusion 0 PB (7-0)

0 Output

Input mode 0 1 0

PC (7-4) Group B

Conclusion 0 1 Mode 1

Channel A can operate in any of the three

regimes, channel B-modes 0 and 1. Channel C

can be used for data transfer

only in 0, while in others he is

for transmission of control signals that accompany the process

of exchange through the channels A and B. D7 discharge control

word (Figure 3) defines a set of operating modes of channels

(D7 = 1), or work in the PPI mode set / reset individual bits

of the channel C (D7 = 0). When bitwise channel management

C level D3-D1 define the number of modified discharge,

discharge D0 sets the reset (D0 = 0) or set (D0 = 1) of the

modified discharge; bits D6-D4 are used. Set / reset bits of

the channel C can be used to generate interrupt request signals

from the PIP. For each of the channels A and B in the PPI has a

trigger resolution interrupt set / reset control word which the

installation / reset some of the discharge channel C. If a

trigger interrupt enable the corresponding channel is set (INTE

= 1), PIP can generate interrupt request signal when ready to

external device input or output.

Mode 0 is used for synchronous

or programmatic organization asinronnogo exchange. Chip can be

viewed in this mode as DEVICE consisting of four ports (two

8-bit and two 4-bit), regardless of custom in

input or output. Conclusion informations carried by the command

OUT microprocessor with fixing output information in the

registers channels, and input-team-IN without memorizing

information. Mode 1 provides a gated one-way information

exchange with the outside DEVICE. Data transfer is performed by

channels A and B, and C of the channel uprovlyayut

transmission. Channel operation in Mode 1 is accompanied by

three control signals. If one of the channels programmed in

Mode 1, then the remaining 13 interface lines can be used in

mode 0. If both channels are pre-programmed to Mode 1, the

remaining two front-line of the channel C can be

configured for input or output.

In mode 1, for information used

The following control signals: gate admission

(STB)-input signal is formed by an external

device, indicating a willingness to VU

input information; acknowledgment (IBF)

-Output PPI telling BY the end of the receiving STB; interrupt

request (INTR) -Output PPI, which informs the MT of

completion of data reception in the channel; Nuroven signal is

set at STB = 1, IBF = 1 and INTE = 1; reset signal decay RD.

For input control signal

INTE A channel is carried out through PC4,

and B-channel through PC2.

To display information vrezhime a ispolzuyutsa following

control signals: strobe write (OBF)-output signal to indicate

external device's readiness to conclude;

formed on the front of WR; confirmation

write (ACK)-input signal from the external

DEVICE, confirming receipt of information

of FDI, an interrupt request (INTR)-output

TTR signal, which informs the completion of the MP

Operation information output; H-level signal is installed at

the front signal ACK for OBF = 1 and INTR = 1; reset recession

signal WR.

P.S. Continued in the next issue.

typed text (GAME BOY)

Other articles:

Similar articles:

В этот день... 30 March