|

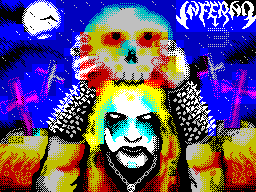

Inferno #03

22 ноября 2002 |

|

Diploma - Diploma Alone Coder-a. Development of software for special logic analyzer. Part 1.

Abstract

In the capstone project on the topic: "The software

specialized logic analyzer (ALS) has developed management

programs and self-control of ALS on based single-chip

microcomputer AT89C52, and also exchange data with PC via an

interface RS-232 with software compression.

ALS is working with the management

PC for the issuing of the results read on the screen and record

it on magnetic media.

Functional diagram of the device, the description of

algorithms and software programs themselves, the creation and

justification of the method of data compression, as well as

testing technique developed software and performance evaluation

programs are given in settlement memorandum.

Software developed in Assembler,

Compiling and Debugging held by

Package Asm51Edit 2 + Debugger-51.

This software is included in the

of the software system developed by the scientific and

technical department of the Federal State Unitary Enterprise

RCB <Globe>, which was created diploma

project.

Summary

In given degree project on a theme:

"Software of specialized logic analyzer

(SLA) "has been developed program of management and

self-checking and data exchange with PC by interface RS-232

with a program compression.

SLA is based on microcontroller AT89C52

and works together with manager personal

computer, which can view results on the

screen and record them onto magnetic disk.

Functional scheme of SLA, description of

algorithms and programs, compression method

creation and explanation, testing methods

and examination of results of work of programs - are given in

an explanatory note.

The software is written in ASSEMBLER

language. Compilation and debugging are

carried out with the help of package

Asm51Edit 2 + Debugger-51.

The given software is a part of the

program complex, which is being developed

by a scientific and technical department

of design office "the Globe" where the degree project was

created.

Contents

1. Introduction .............................. 4

2. Feasibility Study ..... 6

3. Statement of the Problem .................... 10

3.1. Principles for building an ultralight ............ 10

3.2. The block diagram of ALS .............. 14

3.3. The command system of ALS ................. 21

3.4. Develop requirements to the program .. 30

4. The theoretical part of .................. 36

4.1. Timing measurement ........... 36

4.2. Selection and justification of

Development .......................... 48

4.3. Development of general and detailed

algorithms of the program ................ 50

5. The practical part of ................... 57

5.1. Features of development programs

for OEVM ............................ 57

5.2. Development and description of the program

for OEVM ............................ 60

5.3. Standalone debugging program

Model .............................. 68

5.4. How to work with ALS .............. 76

6. The economic part of .................. 79

6.1. Defining complexity of development

software ............... 79

6.2. Building a ribbon graphics ...... 82

6.3. Estimating the development .... 83

6.4. Conclusions on cost-effectiveness

software ............... 86

7. Safety and environmental proekta.87

7.1. Analysis of working conditions in the premises

with PC .............................. 87

7.2. Selecting the method of conditioning

room with PC .................... 94

8. Conclusion ........................... 99

9. Literature .......................... 100

10. Applications ......................... 102

1. Introduction

The life cycle of electronic products, produced by the

enterprise, includes the following steps:

■ development of the concept and other necessary design

documentation; ■ manufacturing;

■ control of manufacture;

■ setting;

■ operation.

Design, manufacture and commissioning complex electronic

equipment (REO) unthinkable without the use of

avtomatizatsii.Primenenie various automated systems (AS) can

significantly shorten the product development, to minimize

errors and increase reliability apparatury.V presently a member

of the AU as the controls are widely and effectively used as a

specialized computer and universal computer. Modern personal

computers for various speakers have acceptable parameters, such

as high speed (Hundreds of millions of operations per second),

a large amount of memory (hundreds of megabytes), the

possibility of long-term storage large amounts of information

on magnetic and other carriers, the ability to exchange data

with external devices at high speed, multitasking, etc. It

became possible to implement algorithms that have previously

almost could not be implemented because of lack of memory

capacity and speed.

The process of creating a modern electronic equipment is

complex and accumulates errors at all stages. Part of the error

is detected only after a build, in phases

control of manufacturing and setting are already operating

device.

It is therefore important in the production equipment has

debugging process of setting up and operation.

A large number of instruments and devices used in the

enterprise RCB <Globe>, focused on a common bus connection type

MMI. Adjustment of devices connected to the bus MMI requires

the use of logic analyzer. Logic Analyzer - a measuring

instrument, a function which is the removal of the timing

charts of digital signals (hereinafter - the measurement) with

a time-bound withdrawal timing chart at the time of occurrence

of certain combinations of signals (synchronizing combination).

The need for a logical

Analyzer (LA), as well as focus on the basic design decisions

predpriyatiyaizgotovitelya required the development of

specialized aircraft (ALS) in the construction business.

An integral part of automated

debugging the equipment, based on

ALS is a software

core devices - single-chip microcontroller, which supports

management of the hardware monitoring and dialogue with PC.

Development of such software, and is dedicated to this

thesis project.

2. Feasibility

rationale for developing

In the large enterprise shops

often required to implement centralized control and management

of multiple devices.

On Federal State Unitary Enterprise RKB <Globe> developed

specialized intermodule interface (MMI) oriented to connect to

one bus a number of devices and control their behavior with the

mainframe.

Debugging devices connected to the bus

MMI, requires special equipment, such

as digital storage oscilloscopes or

logic analyzers. Localization error

in each device with manual control

(Functional testing) can take

several days, while special equipment can find the same error in

within a few hours or minutes.

Logic analyzers, in this case

preferable because of the large number of simultaneously

observed signal lines, which makes it possible to trace the

interaction processes signals according to from each other in

terms of their aperiodic education. Identification of some

errors of schemes devices is almost impossible without the

simultaneous observation of the majority of the signals. For

example, pairwise comparison 32 MMI interface signals on a

two-beam oscilloscope includes 32.31 / 2 = 496 measurements

with different probe position, whereas logic analyzer can

perform the same problem for 1Ў3 measurement, depending

the number of simultaneously analyzed lines

for the aircraft. In this case, the logic analyzer has the

ability to automatically synchronize to some combination

signals generated on the bus, which allows avoid manual

analysis of long sequences of recorded signals.

Produced in series logic analyzers are described, for

example, [7], because its stationarity is difficult to use for

monitoring equipment in the existing shop. Moreover, conditions

in the shop often do not meet performance characteristics of

the device, which can lead to its incorrect operation or

malfunction. So the best solution would be handheld

a dedicated logic analyzer

(Ultralights), dividing the functions of a computer, as

which may be a modern personal computer equipped with a serial

RS-232 to communicate with ALS on twisted-pair. A full

display installed on a PC, allows

reduce the complexity of visual work

operator of ALS, and a powerful central processor enables PCs

to implement algorithms computer analysis of the removed signal

sequences. When using the bank of reference signals can

completely automate the process of testing to the standard

equipment.

Specialized logic analyzer differs in that its connection to

bus will be the only way to help boards being placed in one of

Slots intermodule interfeysa.Eto avoids a lengthy process of

placing probes on the signal conductors, paired with errors

that can not only lead to incorrect measurements, but also to

burnout test equipment.

When the above system design

ALS - PC device ALS should be the most prostym.V Currently it

allows to achieve the use of SoC technology

mikroEVM.Sovremennye microminiaturization allowed to place on a

single chip CPU, ROM, RAM and controllers of access to external

ports.

Microcontrollers MCS-51 family (domestic counterparts - the

family MK51) were popularity among other microcontrollers

because of particularly good architecture, convenient for the

design based on her various devices. Has proved useful to use a

portable ALS chip AT89C52, compatible with MCS-51, but reflect

greater performance, increased in comparison with their

predecessors RAM and ROM, as well as an improved mechanism for

synchronization.

Since the process of removing the signals specialized logic

analyzer has to produce at high frequencies

(Up to 5 MHz), for which no

fit the selected microcontroller, you need to mount in the same

device SRAM with the scheme of automatic

write to one of the tires of MMI. In this scheme

records must be controlled programmatically

software controller AT89C52, which

in turn, must execute the commands

transferred to the control program running on a PC.

Also, the microcontroller must perform periodic health check

of ALS RAM (self) and encoding data (with compression and error

protection) transfer them to the PC via an interface

RS-232.

A significant factor influencing the time

development described above, ALS is

design-time control software

ensure mikrokontrollera.Eto time is significantly reduced

through the use of specialized cross-development tools:

krossassemblerov, debuggers, and in-circuit emulators, etc.

Conclusions:

1. Any device after assembly may contain errors that can be

localized with debugging at the stage of operation.

2. Fittest device

debugging devices connected to a common bus type MMI, is a

specialized logic analyzer (ALS). 3. The portable part of the

SLA should be compact, which is achievable with modern

technologies (single-chip microcomputer, in future - OEVM).

4. Necessary software for

management microcontroller - the core of ALS.

5. Should apply specialized

cross-development tools and debug software ALS.

Requirements for the product:

1. The program should provide specialized management board

logic analyzer. 2. The program must be placed in ROM

Microcontroller AT89C52 (volume of 8 kilobytes).

3. The program needs to communicate

with PC via serial interface

RS-232 with a speed of 19200 baud.

4. Format parcels between ALS and the PC should

comply with standards adopted by

enterprise.

5. The program must perform the following

main functions: starting and stopping measurement task

measurement modes, transfer measurement data on PC,

self-control and issuance of state of the logic analyzer.

6. All actions should be carried on

commands sent from a PC.

3. Problem Statement

3.1. Principles for building an ultralight

Depending on the implementation of logic analyzers can be

divided into two Class:

■ fully implemented by hardware;

■ controlled by a PC.

In the case of a hardware implementation of opportunities

for interaction with the operator, the organization of files

and protocols significantly limited. An example of

hardware-based aircraft are devices Thandar TA 2080, Soar 1420,

Racal Dana 202 [7]. The implementation is integrated with the

control PC has the following advantages:

■ developed a means of user interface, allowing the operator

to organize the interactivity with the control PC;

■ opportunities for storage and

editing of documents accompanying

process of adjustment;

■ reducing the time required for the introduction of the

original data; ■ the possibility of implementing complex

control algorithms; ■ High flexibility;

■ the possibility of interaction

Database;

■ possible through automation, interfacing with CAD systems,

etc.

In this diploma project is developed specialized software

logic analyzer, integrated with an IBM-compatible PC.

Description structure and operation of the device are shown in

Sections 3.2 and 3.3 of this diploma

project.

Develop specialized logic analyzer (ALS) is composed of two

parts: a portable unit with a commuting

connector (plugs with jumper), intended for connection to the

bus MMI, and stationary computers total naznacheniya.Dve parts

are interconnected by bus cable with a serial protocol for

standard RS-232 frequency of 19200 bps.

The portable part of the ALS is based on single-chip

microcomputer AT89C52 and operated program in the language

ASSEMBLER.Dannaya program should handle the requests received

through the channel PC-ALS, and depending of these requests: to

control the work recording and synchronization schemes, placed

on the same portable part, return the data in compressed form

to the main Computers, as well as to produce self-schemas

devices on the team and for inclusion.

Recording scheme, and synchronization work

separately from the microcontroller, but to manage it. It

provides data on logic levels on the bus with MMI high

(Up to 5 MHz) sampling frequency,

which is impossible by means of the microcontroller AT89C52.

Scheme of records contained on a portable

parts, writes to dual-port RAM

(Dose) of arbitrary cross-connected 32

MMI bus lanes with a sampling frequency defined by a

programmable counter-taymerom.Pri This division ratio of base

frequency, which yields a sampling frequency of recording

signals in the dose given command of the microcontroller.

The scheme of synchronization with the control unit starts

and stops scheme records in RAM after the bus

certain combination of logic levels

signalov.Sinhroniziruyuschim can be of any

set of 16 signals shiny.Sinhroniziruyuschy

set of signals given by the microcontroller

in the form:

■ 16-bit mask participating in the comparison

signals;

■ 16-bit polarity involved in comparing signalov.Polyarnost

signals outside the mask, when compared to the synchronization

is not considered.

Unlike an oscilloscope, which usually starts at the first

crossing of a predetermined threshold, the aircraft may have

multiple modes running [7]:

■ Start with the appearance of the word

data, ie analyzer is triggered when

inputs form part of a combination of data;

■ pre-launch / poslezapusk used

to remember, and if necessary, and the input data indicating

that came before the launching of speech and after it; ■

Start-up, when there is a definite difference between the

expected signals and received input data, etc.

Developed ALS should work

several modes of synchronization run:

clock signal occurs at the beginning / before the read sequence

(span), or at the end this interval, either in the middle.

Therefore, synchronization scheme can start reading before the

synchronization combination or some time thereafter. With the

help of other programmable counter-timer is given time off

delay circuit record. Time delay start / Stop recording scheme

is given in units of the microcontroller AT89C52 sampling

period are read.

Used chip RAM has a capacity of

16 Kbps (for storing up to 4096 readings

32 channels). Wiring diagram of the RAM

is a conditional two-port, ie, to her

access scheme and the recording and mikrokontroller.So by

recording scheme has 12razryadnaya address bus and 32-bit data

from the microcontroller - 14razryadnaya address bus and 8-bit

data. DOSE is located in the address space of the external

memory OEVM in lowest address.

All measurement parameters (type of synchronization,

synchronizing the combination, the number of points of the

interval measurement, sampling, etc.) are specified by the

operator and the main PC to be transmitted to the SLA on a

serial interface together with a command or query. ALS software

must interpret and execute commands and requests filed with the

PC, and return on the serial interface

data on the results of execution.

PC, which manages automated debugging of equipment based on

ALS, should display the read sequence of logic levels of

signals and display these signals in the form of a graph.

For management of ALS can be used almost every model of PC,

equipped with a graphic display, archival memory and serial

interface RS-232.

The device of ALS, but also based on

It debugging equipment detail

considered in the next section.

3.2. The block diagram of ALS

Specialized logic analyzer controlled by a PC consists of two

main components:

■ LA (ALS);

■ Leading (control) computer.

The block diagram of ALS with control

PC is shown in Figure 3.2.1.

PC OPERATOR

RS-232

| |

OEVM SH.UPR

| |

| |

RAM SH.ZAP

| |

ALS MMI

Yi

Ris.3.2.1. The block diagram of ALS.

The scheme marked by:

■ OEVM - CPU ultralight, single-chip microcomputer AT89C52;

■ PC - Control PC connected to

ALS using a serial interface

RS-232;

■ yi - debugged device connected to the bus;

■ MMI - MMI common bus (intermodule interface);

■ Sh.Upr. - Account management scheme in

RAM;

■ Sh.Zap. - Scheme of automatic recording

in the RAM data, taken from the bus MMI.

Functional diagram of the device depicted in Figure 3.2.2.

[Prim.izdateley: here was a scheme in landscape layout,

sm.grafichesky material]

Ris.3.2.2. Functional diagram of ALS.

The scheme designated (in addition to the described

above):

■ P0, P1, P2, P3 - bi-directional ports

OEVM for connecting external devices;

■ SHA - address bus;

■ SM - Data Bus;

■ WR - recorded signal to external memory,

generated OEVM;

■ RD - a signal read from external memory

generated OEVM;

■ ALE - strobe negative momentum generated OEVM transfer the

high part of address through port P0 when accessing external

memory; ■ TM1, TM2, TM3 - incremented counter-timers with a

programmable division factor of the base frequency. Controlled

pulse increment (+1). Because the counters run continuously,

the resolution transmission of the generated pulses of overflow

(OV) manages control scheme; ■ MMI - MMI with a common bus

connected debuggable devices Y1, Y2 ,..., yn.

■ TS - Schmitt trigger;

■ RG - buffers registers. OE - allowing input, controls the

third state of the output register. C - input pulse records in

the register; ■ DOSE - dual-port RAM, which accumulate

data on the logic levels of signals for

measurement period. OE - allowing entry.

WE - write enable input of RAM. From the OEVM DOSE decrypted

when A15 = 0; access to other devices implemented with A15 = 1;

■ Self-control - a route on which at

test value of ALS from the outputs of address counter are

supplied to kommutator.Eto allows a self-input channels ALS

after assembling the device; ■ F1 - clock.

Addressing devices on the internal bus

Address ALS has two simultaneously set bits addresses. Complete

device addresses are shown in Table 3.2.1.

Table 3.2.1

Device Address

Significant bits of the word polarity

sync combinations 0C000h

Significant bits words polarity

sync combinations 0A000h

Significant bits of word sync configuration combinations 09000h

Significant bits word sync configuration combinations 08800h

Initial state schetchikataymera TM1 (article) 08400h

Initial state schetchikataymera TM1 (Jr.) 08200h

Initial state schetchikataymera TM2 (article) 08100h

Initial state schetchikataymera TM2 (Jr.) 08080h

Initial state schetchikataymera TM3 (article) 08040h

Initial state schetchikataymera TM3 (Jr.) 08020h

Code switching devices 08010h

When "0" in the words of the discharge configuration -

channel is not involved.

When "1" in the words of the discharge configuration -

channel is activated.

"0" in the words of the polarity of the discharge - the

polarity of the signal "+".

"1" in the words of the polarity of the discharge - the

polarity of the signal "-".

Device switching commutes with a set of jumper bus line MMI

32 channels, numbered 0 .. 31, and returns

code of commuting Jumper

validation connect the

to the bus.

All counters, timers, 16-bit and work on the growth rate.

Overflow (OV) in counters, timers, generated during the

transition from 0FFFFh to 0000h.

Address space of RAM (16 kbytes)

divided into four regions as follows

read (ris.3.2.3):

3FFFh

These channels

3000h 24 ... 31

2FFFh

These channels

2000h 16 ... 23

1FFFh RAM

These channels

1000h 8 ... 15

0FFFh

These channels

0 ... 7

0000h

Ris.3.2.3. The distribution of data channels

in RAM.

In each of these channels are distributed on the bits of

bytes of RAM, as shown in Table 3.2.2:

Table 3.2.2

Bit0 Bit1 Bit2 Bit3 Bit4 Bit5 Bit6 Bit7

K.31 K.30 K.29 K.28 K.27 K.26 K.25 K.24

K.23 K.22 K.21 K.20 K.19 K.18 K.17 K.16

K.15 K.14 K.13 K.12 K.11 K.10 K.9 K.8

K.4 K.5 K.6 K.7 K.3 K.1 K.2 K.0

Protection circuitry protects the ALS exit

failure due to the possible occurrence of large

stresses on the bus in case of breakage kakogolibo MMI device

connected to the bus.

The work of ALS in the following manner.

On command <Original> ALS from PC to reset sostoyanie.Dlya

setting the initial state forms of ALS The following control

signals:

■ - resets the trigger circuits control the timing

records in RAM; ■ - reset signal is forced shutdown

control circuits.

In addition, given the initial state the serial port RS-232.

When a request is ALS programs all

schetchikitaymery specified in the query coefficients division,

puts in a word and configuration word of the polarity of the

desired type of sync combinations, and then creates the

positive momentum to start management scheme.

The control circuit for clock signals

counter TM1 sends a gating pulse

buffers to the register entries in the RAM, after

Why register on the outputs generated a stable combination of

logic levels 32 signals intended for recording and

gives impetus to write the appropriate

input RAM.

TM2 delay counter starts to run the comparison circuits and

guarantee entry in RAM, the required number of samples of

information about the channels until you sync kombinatsii.Eto

required in sync, at which the synchronizing combination should

occur in mid- or the end of measurement interval.

Count of the number of points TM3 determines how many

samples logic levels channels will be written after the

appearance of bus sync combinations. After

This scheme records into RAM automatically shuts off.

Timer values can be represented by

next Timeline (ris.3.2.4):

SC

written information is t

>

<T2> <T3>

<>

number of points

Ris.3.2.4. The initial values

counter-timers.

Here:

■ UK - the moment of occurrence sync

combination;

■ T2 - inverted primary content

counter-timer TM2 (as the timer runs on the growth rate);

■ T3 - inverted primary content

counter-timer TM3;

If you specify a form of ALS launch delayed

after receipt of sync combinations, while the delay measured in

strokes recording scheme includes (added with opposite sign) in

the initial contents of TM3.

Starting address read to the RAM is not defined, so a read

request memory and channels provided field start address for

reading, and the request <Read state LA> PC returns the current

state of the address counter.

3.3. The command system of ALS

To control the operation of a specialized logic analyzer with

PC must be provided for several

types of commands and queries that are sent via RS-232. For

shipment in PC data assume that the sequence of signals ALS

should provide appropriate responses (OS).

Formats of input and output messages

for ALS developed FSUE RKB <Globe> and

indicated in the technical task of development.

Information via the RS-232 transmitted frames. The exchange

is made at 19200 baud, 1 stop bit, 8 data bits no parity

control.

Frame structure is shown in Table

3.3.1.

Table 3.3.1

№ bytes Appointment

An operation code (CPC)

2 (inversion CPC) + 1

3 Number of bytes of data item. (Nst)

4 Number of data bytes ml. (Nml)

5 bytes of data 1

6 bytes of data 2

... ...

N +4 data byte N

N +5 checksum

Bytes 3Ў (N +5) - optional, they are present in the frame,

if 7-bit code operation is 1.

Checksum - add up to 28

sum modulo 2 bytes 3Ў (N +4).

Opcodes commands, requests and OS are shown in Table 3.3.2.

Table 3.3.2

Bits CPC Name

76543210 hex

Encoding Opcodes

commands and queries

00000001 01 Team <Original>

10000010 82 teams

00000011 03 Team

00000100 04 Team

00000101 2005 Request

<Read the state of LA>

10000110 1986 Request <Read RAM>

10000111 87 requests <Read channel>

Encoding Opcodes

Response

10000001 81 OS

00000010 02 OS

00000011 03 OS

<Error Data>

00000100 04 OS

00000101 05 OS

ALS provides the OS, if:

■ bytes 1 and 2 made no errors;

■ byte value 2 is the growth rate of inversion value byte 1;

■ adopted a valid CPC.

Otherwise, the OS is not issued.

ALS provides OS:

■ or if taken without error

correct command or request;

■ <Error Data> if an error is detected when receiving byte 3Ў

(N +5) or did not match the checksum;

■ if taken

incorrect data;

■ if passed incorrect CPC.

PC repeats the issuance of a command or request to M times

in the following cases:

■ there is no OS for T seconds;

■ encountered an error when receiving byte

1Ў (N +5);

■ did not match the checksums;

■ adopted OS <Error Data>.

Repeated or a new command or query

must be issued no earlier than t seconds after taking the OS.

Exchange parameters by default:

■ M = 4;

■ T = 4;

■ t = 0,1 sec.

The following are the formats of commands and prompts the

leading PC and the actions ALS performed in accordance with the

format received the command or request, and formats of the OS.

a) Team <Original>.

Table 3.3.3.

Command format <Original>

№ bytes Appointment

1 CPC

2 (inversion CPC) + 1

By this command:

■ issued a ;

■ Microprocessor module ALS is set to its initial state;

■ self-satisfied microprocessor unit ALS and the external

memory; ■ formed the word state of the aircraft.

b) Team .

Table 3.3.4.

Command format

№ bytes Appointment

1 CPC

2 (inversion CPC) + 1

3 Nst

4 Nml

5, the word configuration item.

6, the word configuration ml.

7, the word polarity of Art.

8 words polarity ml.

9 is running

10 Number of measurement points

1911 measurement period art.

12 ml of the measurement period.

13 Number of cycles delay station.

14 Number of cycles delay mL.

15 Checksum

By this command:

■ reset the status byte LA;

■ downloaded relevant registers

LA;

■ start the admission process sinhroslova

or measurements;

■ formed the word state aircraft;

■ issued a .

c) Team .

Table 3.3.5.

Command format

№ bytes Appointment

1 CPC

2 (inversion CPC) + 1

By this command:

■ terminate the admission process sinhroslova or measurements;

■ LA prepared for the next launch;

■ formed the word state aircraft;

■ issued a .

d) Team .

Table 3.3.6.

Command format

№ bytes Appointment

1 CPC

2 (inversion CPC) + 1

By this command:

■ issued a ;

■ self-satisfied LA;

■ formed status word on the results of self-control aircraft.

OS is issued before the operation to the PC can monitor the

successful reception of the team. The following command or

query may be issued no earlier than Tsmk

(To be determined in due course

after the development of the program LA). Default: Tsmk = 800

ms (time of the self-RAM and ROM).

e) Request <Read the state of LA>.

Table 3.3.7.

Request Format <Read the state of LA>

№ bytes Appointment

1 CPC

2 (inversion CPC) + 1

For this request:

■ given status word in the frame LA OS

;

■ reset ranks number number 0, 1, 2, 3 bytes

the state of LA.

Table 3.3.8.

OS code on request

<Read the status>

№ bytes Appointment

1 CPC

2 (inversion CPC) + 1

3 Nst

4 Nml

5 bytes of the state of LA

0p .= 1 refusal self-RAM

initialization

1p .= 1 refusal self-ROMs

initialization

2p .= 1 refusal self-RAM

3p .= 1 refusal self-ROMs

4p .= 1 expectation sinhroslova

5p .= 1 expectation of the end

measurement

6p .= 1, data in RAM ready

for extradition

7p. Reserve (0)

6 Code switching devices

7, the word diagnostic item.

8 words diagnostics ml.

9 State of the address counter st

10 state of the address counter ml

1911 Reserve (0)

12 Checksum

e) Request <Read RAM>.

Table 3.3.9.

Request Format <Read RAM>

№ bytes Appointment

1 CPC

2 (inversion CPC) + 1

3 Nst

4 Nml

5 Number of channels:

0 - (0-7) channel

1 - (8-15) channel

2 - (16-23), the channel

3 - (24-31), the channel

6 Number of initial bytes of Art.

7 rooms start byte ml.

8 The number of bytes of Art.

9 the number of bytes ml.

10 Checksum

For this request:

■ given a specified number of bytes from

specified number of bytes in a given group

RAM Aircraft operating in the frame .

Table 3.3.10.

OS code on request <Read RAM>

№ bytes Appointment

1 CPC

2 (inversion CPC) + 1

3 Nst

4 Nml

5 bytes of RAM, a

6 bytes of RAM, 2

... ...

N +4 N bytes of RAM

N +5 checksum

g) Request <Read channel>.

Table 3.3.11.

Request Format <Read channel>

№ bytes Appointment

1 CPC

2 (inversion CPC) + 1

3 Nst

4 Nml

5 Channel number

6 Number of initial bytes of Art.

7 rooms start byte ml.

8 The number of bytes of Art.

9 the number of bytes ml.

10 Checksum

For this request:

■ Choose the most efficient method

compression / encoding data

desired channel;

■ in a compressed / encoded form issued

specified number of bytes from a given number bytes for a given

channel of RAM LA in the frame OS .

When you send a chosen method of compression /

data coding, the most profitable for

the volume of parcels (transmission time) in this

sluchae.Vybor specific compression method is performed on

Statistics of fronts (Compression techniques discussed in

section 4.1: <Timing Measurement>).

Table 3.3.12.

OS code on request <Read channel>

№ bytes Appointment

1 CPC

2 (inversion CPC) + 1

3 Nst

4 Nml

5 methods of compression:

0 - constant signal 0

1 - Permanent signal 1

2 - signal with no compression

3 - signal is compressed by

bit RLE-method

6 bytes of a data channel

7 bytes of data channel 2

... ...

N +4 B N-1 data channel

N +5 checksum

These formats of commands and queries as

must be supported by the program management computer.

3.4. Develop requirements to the program

Based on the above formulated the following requirements for

program management of specialized logic analyzer.

The program shall maintain the following

stages:

1. receiving a command or request from the management

PC;

2. Preparation for measurement;

3. waiting for synchronization of the combination;

4. wait for the measuring and reading

Data Bus MMI in RAM;

5. data transfer to the control of ALS

PC;

6. self-control modules ALS;

7. setting the initial state and initialize modules ALS.

Receiving a command or request from the management

PC

Program management specialist

logic analyzer must produce

All of the commands sent from

PC. The program should expect to command or

query is always, except for time

she is not busy with other tasks, such as

self-control or data transmission.

In receiving a command or query

program must provide:

■ input validation for correctness;

■ in the case of correct reception of the frame program should

handle any given command and issue a reply message or ; ■ In the case of erroneous

reception of the frame (invalid length or mismatch control

amount) the program should give the OS <Error Data>;

■ in the case of incorrect input data

program should give the OS .

Preparation for Measurement

The beginning of the measurement should be initiated

operator controls the PC. When you receive the command management program must initialize the ALS counters,

timers and comparison circuit in accordance with those in

command data, and then apply to the input control circuit

positive momentum .

After that the program should be transformed into

Standby new request or command

with the control computer.

Measurement can be forcibly interrupted before its

completion when applying the operator controls the PC team

. In response to this command management

program must apply for ALS input control circuit positive

momentum .

Waiting for sync combinations

After starting the measurement, prior to

synchronizing a combination of ALS management program should be

in the loop standby command or request a personal computer. In

response on request <Read the state of LA> Program

should be in the running to return the body of information about

that LA is in standby mode

sinhroslova (set 4-th digit of the status byte LA).

Information about finding a LA Mode

expectations sinhroslova allows the operator to

Personal computer monitor <hang> LA (at

Waiting is not possible, for example, mistakenly

introduced, the synchronization combination) and

take a decision on compulsory termination of the current

measurement.

Waiting for the end of the measuring and reading

Data Bus MMI in RAM

During the measurement, after the receipt of

synchronizing a combination of ALS management program should be

in the loop standby command or request a personal computer. In

response on request <Read the state of LA> Program

should be in the running to return the body of information about

that LA is in standby mode

end of measurement (set 5-th digit of the status byte LA).

In sync after receiving sinhroslova begin automatic recording

in the RAM data bus channels MMI.V other modes of

synchronization record in the RAM starts up

sinhroslova.Poskolku expectation records in RAM requires the

introduction of the scheme has a counter, in the implementation

of ALS entry in the RAM starts to sinhroslova in all modes of

synchronization, but used only useful data is considered the

last. When recording an increase of addresses are cyclically

within each of the 4 areas of RAM.

Measurement is considered complete when

RAM is read by the required number of samples

useful data about the channels.

After completing the measurement circuit record

in RAM is disabled and the request <Read the state of LA> the

program should return information about the successful

completion of the measurement (Set 6-th digit of the status byte

LA). Of bits 4,5,6 of the status byte LA at the same time can

only be installed one.

Transferring data from an ultralight to the control

PC

Once the request <Read the state of LA> the PC will receive

a reply message containing information about the measurement is

finished, the PC may file a request for extradition measurement

data.

Program management of ALS should provide two modes of

transmission of the channels on PC: Each channel

simultaneously.

In the case separately to each transfer program

Management of ALS on request <Read channel>

returns in a compressed form of the required number of bytes of

data on the state desired channel stored in the RAM with ALS

specific address.

In the case of simultaneous transmission of a single query

PC <Read RAM> Program Management of ALS returns data

immediately about 8 adjacent channels, located in one area

OZU.Szhatie is not performed.

Self-control modules ALS

Self-monitoring of ALS is made immediately after the reset /

enable and team-PC <Run self-LA>.

Control program checks for ALS

the truth of the contents of internal ROM and

tests the performance of the external RAM.

At the time of self-control (Tsmk = 800 ms) of ALS are not

handles the message management computer.

Self-monitoring of memory produced by

control and sequential filling

RAM from the top down and bottom-up values

55h, 0AAh, 00h.

Self-control ROM is signature analysis: by comparing the

signature Rom, recorded in the last 19 bytes of ROM

(16 byte signature + 3 bytes of

amount), with the signature, calculated on the basis of

actual content of ROM. Signature

computed for each bit separately,

polynomial basis:

16 12 9 7

X + X + X + X + 1.

The efficiency of the input path and

recording scheme in the RAM is made by

institutions address counter outputs to the input switch, then

control the PC the general procedure can read these signals at

the request of ALS.

Setting the initial state and initialize modules ALS

Program management of ALS found in

initial state after reset /

inclusion and team-PC <Original LA>.

In the transition to its original state program is to

produce self-control and formed on the basis of its results

status word of the aircraft. Configuring modules ALS

initialization is reset signal lines and and

clearing the contents of the dose.

Input

Input data at different stages of the program are:

■ commands and requests issued by SLA to

RS-232 interface in accordance with clause 3.3.;

■ information obtained as a result of self-ALS;

■ information read from the bus MMI;

■ information about the status of ALS received

from the control circuit record in the RAM.

Imprint

Output of the program are:

■ response messages from ALS to RS-232 interface in accordance

with clause 3.3.; ■ signals given by the control circuit;

■ Information to be entered when you start measuring in

meters, timers, and a comparison circuit.

Requirements for the structure and parameters of technical

means

Management program should operate an ultralight single-chip

microcomputer AT89C52 clocked at 24 MHz, connected to

IBM-compatible PC via the serial interface RS-232 speeds

transmission of 19200 baud. Program should be placed in ROM

OEVM of 8 kilobytes.

4. Theoretical part

4.1. Timing measurements

For efficient operation of ALS cycle time

measurement and transmission of its results should be

minimizirovano.Rasschitaem this time.

Raw data:

■ speed data exchange interface

RS-232 (19200 baud);

■ performance OEVM AT89C52: machine

cycle (the time the simple commands)

500 ns at a clock frequency f = 24 MHz;

■ while reading a single quantum state

analyzed lines: 200 ns to 200 microseconds

(In practice, most commonly used operating range from 200 ns to

500 ns); ■ number of analyzed lines in the bus

(Maximum 32);

The total measurement time T is the sum of the following

times:

T = tSelect Tozh + + + Tcht Tpodg + Tper, (4.1.1)

where Tzap - the total time spent

to forward requests from a computer in ALS; Identically -

start measuring the waiting time for synchronization to a

specific combination of signals on the bus; Tcht - time spent

ALS to read and save in RAM data bus lanes MMI; Tpodg - the

time of preparation data to transfer; Tper - total time

spent on the shipment of ALS in a computer

information about the status of the analyzed lines.

In the fragments of time Tozh Tcht + +

+ Tpodg receiving side, waiting for the data, sends the

requests. But while these requests are not Tzap included, since

they all, except the last, do not increase the measurement

time. Last request must come after the preparation of data for

transfer, and itself transfer will be carried into his

receipt.

Tzap time depends on the number of bytes of C,

transmitted in the command and query

for ALS.

Let R denote the rate of exchange between ALS and PC. Since

each byte in sending coded 10 bits (8 data bits, 1 start and 1

stop bit), then

19,200 bytes

R = = 1920. (4.1.2)

10

The total length of queries C can be calculated as the sum

of the lengths of queries containing command, and type of

measurement, method of synchronization, the list of

interviewees signal lines, frequency quantization, as well as

the sum of the lengths of individual transfer requests for each

signal.

Let a PC for ALS to read N = 32

channels referred inquiries:

■ STARTING MEASUREMENT, length 15 bytes;

■ READ STATE LA, length of 2 bytes;

■ 32 CHANNEL READ request, the length of 10 bytes;

When the total length of queries C = 15 +2 +

32 × 10 = 337 bytes:

C

TSelect =, (4.1.3)

R

337

TSelect = ¢ 0.18 (c).

1920

The waiting time start measuring Identically

(In sync early, mid

or the end of the measurement of the arrival of a certain

combination of signals on the bus) is theoretically unlimited,

but in the calculation, we can take it equal to 0.1 seconds.

Transmission time Tper determined by the formula:

Q · N

Tper =. (4.1.4)

8R

Where N - number of analyzed lines

bus.

Tcht time determined by the number of quantization points Q

(max 4096) and the sampling rate f, selected by the operator,

and does not depend on the number of monitored lines.

Q

Tcht =. (4.1.5)

f

We take the average measurement of Q = 4000,

f = 2000000 Hz:

Q 4000

Tcht = = = 0,002 (c).

f 2000000 (Hz)

If the transmission of measurement data to a central

computer takes place without the use of compression, while

Tpodg negligibly malo.Vremya measurement is almost entirely

determined by the time of transfer:

T = tSelect Tozh + + + Tcht Tpodg + Tper =

4000.32

= 0.18 0.1 0.002 0 + 8.6 ¢ (c).

8.1920

Measurement cycle, amounting to a second, not acceptable,

since the operator is forced long wait for evidence (in the

case of a single measurement), and the measurement of cyclic

almost impossible, because the result such a measure would be

composed of widely separated time intervals, not constituting a

complete picture of the processes occurring on the bus.

Transmission time can be reduced in several ways: by

reducing the number of quantization points, or numbers of

analyzed lines, or using compression transmitted data. The

first two methods do not you can always apply, because in most

cases required to read a specific list of signals, no signals

from which can not be sacrificed, and the decrease

number of points will either reduce the resolution of ALS, or

loss of sight of the temporary diagrammy.Poetomu appropriate to

use these methods only as a recommendation to the operator, and

compress the data transmitted from the SLA on the PC.

The choice of compression algorithm (compression)

Data

Examples of graphs for signals arriving by bus (Figure

4.1.1), it is clear that some signals is a high-frequency part

low-frequency, periodic and not part of

is separate pulses, others contain

noise (open) or no change in

the present time.

Ris.4.1.1. Types of signals

coming on the bus MMI.

Compression method should take into account all of these

cases not to make losses in the time (the amount of

information) during transmission.

Compression algorithms can be divided into reversible and

irreversible (loss of information). Last in our case is

unacceptable, because it is necessary to recover an accurate

picture measured signals.

Known groups of algorithms

reversible compression of one-dimensional flow [4,

15]:

1. Use of multiple encoding

consecutive occurrences of a unit of information (RLE - Run

Length Encoding); 2. Removing the redundancy arising from

difference in frequency of use of different

characters (the method of Huffman or arithmetic

coding);

3. Use Replace repetitive

fragments with the help of dictionaries or reference

(LZ - Lempel, Ziv, by author name of the method);

4. Using the predictability of the flow

(Markov chains, contexts);

5. Other methods.

Among other methods can distinguish methods of compression

of analog signals, such as DAKX, including methods of working

with spectrum signal, etc. But in our case

no digital signal is provided to an analog form.

The methods of the fourth group are not applicable to

implementation on OEVM of the requirements for high performance

and memory. We can estimate the timing requirements for the

algorithm for ALS in single-chip micro-computer AT89C52, taking

advantage of the fact that data transfer should take place at

speeds R = 1920 bytes / sec. In this case, the time between

transfer of two adjacent bytes is:

-1 1

t = R = ¢ 0,5 (ms), (4.1.6)

1920

500 (ms)

that equals = 1000 machine cycles

500 (ns)

crystals (MC) OEVM.

Methods of LZ enough raznoobrazny.Bazovy version of the

algorithm requires excessively high costs of memory (several

tens of kilobytes in the amount of RAM in the AT89C52 256

bytes). In our case, apply only methods with a predefined

dictionary (table tokens - symbols that encode multiple data

items). Since kind of coded signals is quite diverse, it is

difficult to propose a set of tokens, which allows to realize

efficient compression of the stream at any size units of

information.

Methods for removing the frequency redundancy

can be used effectively in conjunction with

methods other grupp.Metody this group, applied to a stream

containing samples the digital signal can remove the redundancy

caused by the difference of the frequencies of occurrence of

ones and zeros. This difference is large only for pulse

signals.

In our case the most acceptable methods such as RLE, since

most of them fairly quickly and has low

memory.

Compression using the methods of RLE

Consider the basic method of this group.

It is designed for flow compression with

unit of information (a symbol), close to

size to 1 byte (8 bits). In this case N

occurrences of the character C is encoded by a sequence (Table

4.1.1):

Table 4.1.1. Coding repeats

by the method of RLE.

C C N-2

If the symbol C meets exactly 2 times

row, then the algorithm gives a loss of 1 byte. If the same

character repeated more than 257 times in a row, a sequence

should be split into two or more, coding them as shown above.

Since the ALS must pass binary signals, before using this

and similar methods of signals must be

sgruppirovany.Mozhno offer two fundamentally different ways of

grouping data bits derived from measurements using the ALS.

<Vertical> grouping together in

One byte or word counts of different signal lines, taken in the

same time. <Horizontal> grouping together in one byte (word) is

somewhat neighboring samples of the same signal line.

In our case, the more acceptable the second

way, because <Vertical> group is desirable, firstly, the

presence of the multiplicity of lines, the size of the units of

information (that we can not guarantee, since the number of

lines analyzed is indicated in each case the operator), and

second, the correlation between bits in formed a byte, which is

also generally not performed.

Another method of the RLE group does not lose money compared

with the initial sequence with short repeats of one symbol.

In this method, the compressed sequence

consists of alternating blocks, the first of

which encodes a sequence of arbitrary bytes (contains bytes -

the length of the sequence may be 0, and the data itself), the

second - encodes a repetitive symbol (containing the symbol and

bytes - the number of its repetitions, possibly 0), the next

block - again encodes arbitrary data, etc.

For we are considering the analog

signal bunched <horizontal>

You can refuse storage byte character

in each block, repetition coding, using the fact that recur in

most cases can only bytes containing all zeros, or bits of all

bits unit. The choice between zero and one can make the last

bit last compressed bytes.

It is easy to see that the maximum loss (if compressed

random noise signal) is only 5 bytes for Q = 4096. The data in

this case will be encoded as follows (Table 4.1.2):

Table 4.1.2. Coding

Alternative method of RLE.

The length of the uncompressed Sequential STI 255

Uncompressed (255 bytes)? ... ?

Number of retries 0

The length of the uncompressed Sequential STI 255

Uncompressed (255 bytes)? ... ?

Number of retries 0

The length of the uncompressed Sequential STI 2

Uncompressed data (2 bytes)? ?

The author of this graduation project proposed variant of

RLE, manipulative bitstream.

It will be next. At the beginning of the compressed sequence

indicated the initial state of the signal. In each of the next

byte must be kept a distance between the front of the signal in

bits is equal to zero for further continuation of the previous

signal polarity in the case of a pulse of one polarity than 255

bits.

Synchronizing the transfer is complete

Variant of RLE, encoding the distance between the fronts is

good that the introduction of a restriction makes it possible

to predict the length of the packaged unit on the basis of data

on the number of fronts packaged signal. Restriction leads to a

small loss in compression and the density is reduced to the

partition of the interval measurements on the subintervals

(segments) of length 256 bits at the beginning of each of which

clearly indicates the polarity of the signal in this moment.Pri

The front signal coming among these intervals should coded as

an additional psevdoimpuls length 0 bits. This shows that the

length of the resulting packed sequence is:

L = (1 +8) I +8 F = 9I +8 F (bits), (4.1.7)

1

where I - we know in advance the number of intervals, and

the F - calculated the number of fronts, the signal at the

measurement period, not including fronts, coinciding with the

beginning and end of the interval izmereniya.Ochevidno that in

the absence segmentation of the measurement period (I = 1) the

number transmitted pulse lengths for 1 more

than the number of fronts.

If we consider that the polarity of the signal

beginning of the next interval can be found

as the polarity of the signal at the end

previous interval, including the front

Front psevdoimpulsa possible length 0

bits, the length of the parcel will be:

L = 8I +8 F +1 (bits). (4.1.8)

2

This method is applicable to bad frequency and noise

signals, the fronts in which change more frequently than once

in 8 bit.Dlya such signals packed by this method

get a long block of the original.

So it makes sense to signal compression and transfer it with

ALS on a PC to make counting the number of fronts in this

signale.Protsedura counting the number of edges must be

performed prior to the transfer and is optimized for execution

time due to simultaneous testing eight signal lines in the form

in which they placed in the memory reader.

This operation may take place the following code snippet

(run time depends on the data, but on average 40 MC = 20 s):

...

movx a, @ DPTR / / reading from

inc DPTR / / external RAM

xrl a, R5 / / compare with

/ / Previous count

jz m1_7 / / skip,

/ / If the same

mov b, a

clr a

jnb b.0, m1_0 / / Jump if 0-

/ / Category has not changed

inc Lreg0 / / otherwise increment

cjne a, Lreg0, m1_0 / / induces 16

inc Hreg0 / / bit counter

m1_0:

jnb b.1, m1_1 / / similar

/ / Check for 1-th digit to change

inc Lreg1

cjne a, Lreg1, m1_1

inc Hreg1

m1_1:

...

jnb b.7, m1_7 / / check 7-th

/ / Discharge change

inc Lreg7

cjne a, Lreg7, m1_7

inc Hreg7

m1_7:

movx a, @ dptr / / restore

/ / In the battery current count

mov R5, a / / store in regi

/ / R5 tends to follow-up examinations

...

The information obtained will allow to choose

acceptable method of compression, and for some

methods - and to predict the length of the block after

compression. Data on the block length is important, because the

premise should contain the title its length, it is necessary to

synchronize the end of the parcel to the receiving side.

Synchronizing the transfer is for

other compression methods

In many cases, the above variant of RLE, encoding the

distance between the fronts is not the most efficient on the

quality of compression. Therefore, we can envisage the

possibility of using other compression algorithms.

Since many compression methods

data length of the output sequence

not known in advance, then one must either separate the time

compression of transmission time (which is associated with

increased time measurement of the large preparation time

Tpodg), or in some way to divide the parcel into several parts,

each of which will have its own header and

checksum. In this block mode

transfer all of the parcels except the last, must have known in

advance a fixed length B bytes.

The number of B must be less than the amount of internal

memory single-chip micro-computer, as passed section (block)

the compressed data requires preparation.

The transfer in block mode:

■ The program prepares the first OEVM

block of compressed data for transmission, keeping it in the

internal RAM; ■ In response to a request from the PC is

sending the first prepared block. At the same time in another

buffer prepares the next block to transfer;

■ PC can request transmitted by the unit

repeatedly if it contains

error (loss of sync or incorrect

control code). Otherwise, the PC sends a confirmation signal

that serves as a request for continued transmission of data;

■ The above sequence of actions

repeated until, until you receive confirmation of successful

reception of the last block.

However, due to the large volume of additional data transfer

and the need placed in memory OEVM (256

B) two buffers, this method impractical, although it may be

used in this case.

Based on consideration of the characteristics

various methods of compression for transmission

data signals from the ALS to a PC has been selected

compression method "bit RLE with segmentation.

Pause between transmitted to the shift register is equal to

1000 bytes of machine cycles OEVM (4.1.6). The instruction set

of microcontroller AT89C52 does not allow 256-bit comparisons

of data from external memory during this time (you need at

least 1 comparison for 4 cars cycle for the duration of the

commands in 1Ў2 machine cycles), so the segment size is meaning

to be equal to 128 bits, then the phase signal becomes possible

to encode the MSB transferred bytes.

To avoid ambiguity in the interpretation of zero on the

lower 7 bits of byte (Pulse length 0 or 128), agree to assume

in this case the pulse length equal to zero at the end of the

next segment of 128 bytes, only if the polarity (7-bit)

that momentum is different from the polarity

the previous one.

Thus, each byte of the parcel encodes the length of the

pulse and its polarity (from F impulses and I psevdoimpulsov

zero length or psevdofrontov border segments of 128 bytes), and

the length of a parcel without regard to the title is:

Lpos = I + F (B), (4.1.9)

where Lpos - the length of the parcel excluding the header

length, I - number of segments 128 bits (the number of points

in the range of measurement must be divisible by 128), F -

number of fronts, the signal in the range of measurement, not

counting the edges on the boundaries of this interval.

One should bear in mind that if you calculate the number of

edges in the signal exceeds a certain critical value, then

compression will not be made, and the data channel will be

transmitted without compression. The critical number of fronts

signal in the range of measurement, above which the compression

inappropriate:

Lpos <128 · I,

I + F <128 · I,

F <127 · I, (4.1.10)

where I - the number of segments.

If the number of edges to be equal to zero, then the signal

is at this permanent site, and will only be transferred

signal polarity (1 bit).

Thus, the total measurement time with

using the compression ratio is:

T = tSelect Tozh + + + Tcht Tpodg Tper + = (4.1.11)

N

N · I + ∙ F

C Q -5 i = 1 i

Tozh = + + +2 * 10 Q + (c).

R f R

Using the expression (4.1.11), we construct

plots measuring time of

high frequency signals (ris.4.1.2).

Ris.4.1.2. The calculation results

measuring time:

fsig - the average frequency of the signal; Q - number of

points in the range of measurement; T - total time of

measurement. Solid line - using the implemented compression

algorithm. Dashed line - without using compression.

Dashed line - without the control of the applicability of the

compression algorithm.

4.2. Selection and justification

Development Tools

A program for single-chip microcomputer AT89C52 must provide:

■ high-speed data processing;

■ access to all resources of ALS and OEVM;

■ work with the ports;

■ compressing data during transmission;

■ correct error handling in the exchange

data;

■ small amount of code (a maximum of 8 kilobytes);

Of the existing programming languages

for the microprocessor above

requirements are satisfied by only low-level language ASSEMBLER

whose operators directly asking individual team

OEVM that allows you to implement a program

maximum efficiency in terms of

size and speed. However, to achieve the specified

characteristics programmnogro product under development in

Assembler programmer spends more time than in a high- level.

To simplify programming in Assembler created special design

tools - cross-assemblers and

monitors-otladchiki.Kross-development is the process of

designing the software for one type of computing resources on a

computing system of another species (usually more powerful).

The first of these development tools

(Cross-assemblers) can conveniently

edit Assembly language program that is created using a

full-featured text editor, multiple windows, graphical user

interface, the system of contextual clues, etc., as well as

compile (assemble) the typed text ASSEMBLER directly from the

language into machine code of the microcontroller.

Second - monitors, debuggers - are intended for finding bugs

in the program before flashing her machine code in ROM and

debug these errors Disassembly from native text. In this case,

there opportunity to imitate the work of the microcontroller:

execute individual commands, groups commands, subroutines, to

run the program, but, unlike the real processor may interrupt

the execution of a fragment of the program at any time, view

and edit the contents of CPU registers, memory and ports.

Of several sets of such funds

cross-development software for the design consideration of ALS

was selected an integrated suite of assembler and debugger:

respectively Asm51Edit 2 and Debugger-51 created in the Federal

State Unitary Enterprise RKB <Globe> Minaev AS

Package differs from analogues in a positive way

high-performance, plenty of available options, convenient and

intuitive graphical user interface and advanced system of

content assistance.

4.3. Development of general and detailed

algorithms program

4.3.1. The general algorithm of the program

Requirements for the program

Develops software must comply with the requirements set

forth in Section 3.4, and protocols for data exchange,

described in Section 3.3, deliver high performance, control

error of input data and to consider possible exceptions

(failures, disconnected, defective equipment).

Implementation

In accordance with the above requirements, develops software

to be includes the following software modules:

■ routines self-RAM and ROM;

■ unit initialization;

■ handles error situations;

■ block the interaction with the scheme of control exercised

by starting and stopping measurement; ■ I / O routines,

allowing send and receive pictures messages

RS-232;

■ sub transmission of measurement data

on a PC with compression on the fly> and the necessary software

calculate the statistics of channels recorded in the RAM.

After starting and initializing the program

must go to the main reception of the cycle

and processing of commands and queries according to

flowchart (ris.4.3.1).

(Home)

v

Ban

Interrupt

v

Initialization:

LA, timers,

Adapter

RS-232

v

Self-control:

PROM OEVM

RAM Aircraft

<

v

Receiving Frame

in buffer

Reception

v

,.

,.

Yes, / data. No

v `/ 'v

`/ '

Decoding `/ 'OS Error

and execution of the transfer>

CPC Data

v

,.

,.

, / Data. No OS

> "Incorrect>

`/ 'Data'

`/ '

`/ '

Yes

v

,.

,.

, / Need. No OS

> Data>

`Data? / 'Extradited'

`/ '

`/ '

Yes OS

> Team

executed "

Ris.4.3.1. Enlarged BSA

the main loop of the program.

4.3.2. Development of detailed algorithms

program

Of all the developed algorithms included in the software

special logic analyzer in detail in the first place

algorithms need the most important and complex actions, namely:

■ treatment team ;

■ delivery channel data with compression on the bit RLE with

segmentation.

Processing algorithm for

This algorithm is implemented as a subroutine, which is

based on the data block command NeuStar

performs the required initial values of counters, timers, and

runs the scheme management record in memory.

In verbal form, this algorithm can

be represented as follows (the contents of external memory

address DPTR denoted as {DPTR}):

1. Add to the global variable olddptr

(Start address of previous request

read channel) value 0FFFFh, so that when

the following query to read the channel there was a new

analysis of the number of fronts. 2. Copy the configuration

synchronization word combinations from the command registers

synchronization scheme. 3. Copy the polarity of the sync word

combinations from the command registers synchronization scheme.

4. Recorded in the register of the initial state

Timer TM1 value of the measurement period,

taken with the opposite sign.

5. Recorded in the variable DELAY from the team

value of the number of cycles of delay.

6. Recorded in the register of the ACC team code

number of points in the range of measurement.

7. If ACC = 0, N = 256.

8. If ACC = 1, N = 512.

9. If ACC = 2, N = 1024.

10. If ACC = 3, N = 2048.

11. If ACC = 4, N = 4096.

12. If a <form startup> is not equal to 0, then go to step 16.

13. Recorded in the register of the initial state

timer TM3 value - (N + DELAY).

14. Recorded in the register of the initial state

Timer TM2 value 0FFFFh.

15. go to step 23.

16. If a <form startup> is not equal to 1, then go to step 20.

17. Recorded in the register of the initial state

Timer TM2 value-N / 2.

18. Recorded in the register of the initial state

timer TM3 value - (N / 2 + DELAY).

19. go to step 23.

20. If a <form startup> is not equal to 2, then go to step 23.

21. Recorded in the register of the initial state

timer TM3 value

0FFFFh-DELAY =-DELAY-1.

If DELAY = 0 in the count of the number of points

gets the maximum value (overflow on the 1 st cycle).

22. Recorded in the register of the initial state

Timer TM2 value-N.

23. Set the signal line to state 1.

24. Reset signal line to 0.

25. Recorded in the status byte LA 0

26. To issue a .

27. Exit the subroutine.

Algorithm output data channel with

bit RLE compression with segmentation

This algorithm is implemented as a program that is based on

the data block query <Read channel> extradite

Data on the PC.

1. Calculate the number of segs as requested bytes divided by

128. 2. If a fractional or segs segs> 32, then go to the

issuance of the OS . 3. Check the number requested

signal. If (signal number)> 31 then go to the issuance of the

OS . 4. Of 4 or 5 bits number of the signal to get

number of external RAM:

obl: = (signal number) div 8.

5. DPTR: = 1000h · obl + (starting address).

6. If DPTR <> olddptr OR segs <> oldsegs,

call p / n front of counting.

7. olddptr: = DPTR.

8. oldsegs: = segs.

9. masker: =

= 100h shr (1 + ((signal number) and 7)).

10. Assign a number of fronts to fronts

the current channel from the table.

11. If the fronts = 0, then go to the transfer

constant signal.

12. blocklength: = segs + fronts +1.

13. If blocklength> segs-16, the transition to

signal transmission without compression.

14. Issue to the serial port of CPC

.

15. Issue-CPC.

16. Reset checksum: csum: = 0.

17. Issue a byte blocklength. Here

and then issuing a byte buffer of the serial port must

accumulate a checksum: csum: = (csum + (B)) mod 256.

18. Issue a low byte blocklength.

19. Put in the serial buffer

Port number method (value 03h) without

standby transmission byte.

20. segbeg: = DPL

(Beginning of main loop).

21. dplbeg: = DPL

(Beginning of the cycle packing within the segment).

22. If ({DPTR} and masker) <> 0 then go to item 33

(Counting one, otherwise zero).

23. Enlarge DPTR, given the loop

within 4k of RAM: DPTR: =

= (DPTR and 3000h) + ((DPTR +1) and 0FFFh).

24. If ({DPTR} and masker) <> 0 then go to paragraph 26

(Exit the loop).

25. If (segbeg-DPL) mod 256 <> 128, then go to paragraph 23

(continuation of the cycle). 26. If ((segbeg-DPL) mod 256 <>

128) OR ({DPTR} and masker) = 0) OR

DPTR = (destination address)

then go to step 31.

27. Wait for the transfer of bytes to the serial port.

28. Issue to the serial port value (DPL-dplbeg) mod 256 without

waiting for the transfer of bytes. 29. Assign the ACC: = 128

(Sign psevdoimpulsa zero length).

30. Go to Step 42.

31. Assign the ACC: = (DPL-dplbeg) mod 256.

32. Go to Step 42.

33. Enlarge DPTR, given the loop

within 4k of RAM: DPTR: =

= (DPTR and 3000h) + ((DPTR +1) and 0FFFh).

34. If ({DPTR} and masker) = 0, then go

to paragraph 36

(Exit the loop).

35. If (segbeg-DPL) mod 256 <> 128, then go to item 33

(Continuation of the cycle).

36. If ((segbeg-DPL) mod 256 <> 128) OR

({DPTR} and masker) <> 0) OR

DPTR = (destination address)

then go to step 41.

37. Wait for the transfer of bytes to the serial port.

38. Issue to the serial port value (DPL-dplbeg) mod 256 without

waiting for the transfer of bytes. 39. Assign the ACC: = 0

(Sign psevdoimpulsa zero length).

40. Go to Step 42.

41. Assign

ACC: = 128 + (DPL-dplbeg) mod 256.

42. Wait for the transfer of bytes to the serial port.

43. Issue to the serial port value of ACC without waiting for

the transfer of bytes. 44. If (segbeg-DPL) mod 256 <> 128, then

go to item 21 (continued cycle of packaging within the

segment). 45. segs: = segs-1.

46. If segs> 0, then go to paragraph 20

(Continuation of the main loop).

47. Wait for the transfer of bytes to the serial port.

48. Issue to the serial port checksum frame:-csum.

49. Exit the program.

Algorithms for other software modules are relatively simple

and therefore will not be considered here.

Other articles:

Similar articles:

В этот день... 8 April