|

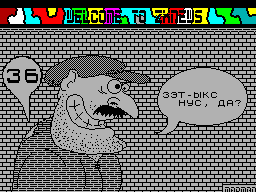

ZX-News #36

02 июля 1997 |

|

processors - Sly processors or programs that are consistently in the same place "hang".

Sly processors

- I told DI: HALT

- So what?

Alexander Mayorov

Dmitry Lomov

You, dear readers, have not met

programs that are stable in one and

the same place, stuck on?

Well, the reasons for this are many, but

another:

Certain program on startup "hung", and

with the question "why?" on Scorpion clicked "Magic" ...

And something happened? Here's what:

Processor executes the command HALT when prohibited

interrupts!

And the same "effect" there was still some programs.

Of course, after the processor

"Pushed" through the HALT, program

earned ...

Since it is unlikely that the authors of the programs "did

not see" this "glitch" when debugging program, the question

"what is it?" it seemed, had no answer ...

It turns out, all due to processor

KR1858VM3. Its interrupt system is somewhat different from

corporate Z80.

Item number one:

In the case of the command HALT ban

interrupt is ignored. That is, the team

DI disables the interrupts and they are impossible

up until the processor does not stumble on

HALT. At the time of execution HALT interrupt

allowed, and as soon as an interrupt occurred, again denied.

Item number two:

While waiting to interrupt on command

HALT is not satisfied regeneration cycle memory. To anything

fatal it does not lead, as the recovered memory video

controller. In the case of a standard processor while waiting

for HALT inside processor generates and executes commands NOP,

and together with them through the cycles regeneration. As a

result, the CPU VM3 register {R} does not change during the

execution of HALT.

Item number three, the previous result:

During the execution of HALT reaction

interrupt when a request is instantaneous. The standard

response to the same CPU interrupt occurs only after the

execution of the current single command NOP.

Ruleznoe consequence of paragraph three:

When writing a multicolor inside a string (for example, the

chessboard), a standard processor to align the entire program,

so during her performance of HALTa HALTa to a multiple of four

(here also need to consider confirmation of the cycle

interruption). If the program does not align

then there are "drozhalki" horizontally

as the time between the occurrence of the interrupt and its

confirmation depends on the phase bypolneniya idle NORov

(irregularity from zero to three cycles). In the case of the

processor VM3 time between the occurrence of the interrupt and

its acknowledgment is always zero (if a HALT). Therefore

processor VM3 indispensable at the stage of debugging

multicolor.

The processor is an analog 1858VM3

Z84C004 (Z80A), excluding the above

circumstances.

That's it!

__________________________

>

Other articles:

Similar articles:

В этот день... 10 April