|

ACNews #17

05 мая 2003 |

|

News - scheme of concurrent interface AY.

nikf

■ ■ ■ ■ ■ ■ ■

■ ■ ■ ■ ■ ■ ■ ■ ■ ■

¤ ■ ■ fix ■ ■ ■ ¤

6.5.2oo3

Now ACE is not only packing himself, but the glue

too! Due to collision with Alexander Mayorov, this possibility

has not tomorrow or after tomorrow, as it is today:)

■ ■ ■ ■ ■ ■ ■ ■ ■ ■ ■

■ ■ ■ ■ ■ ■ ■ ■ ■ ■

- + Of alone coder +

John bought a color TV!

Ldir quite a bit has not had time to collect Last128 # 5 in

April. And then come true would be the promised release of two;)

Inferno # 4 no: (

Again, our Mouzon RAIN8.m no luck - on @ toy he has not got so

same as in Paradox. "Do not reached," they say!

Erase source ANSI0.3 from past sets. GMX does not work there.

But thanks to Nicholas Amoz fixed version, and finally out! But

while you will not see:)

Continued solder adventure!

April 13 came to me again KSA-7G, and then in our bright

heads ripe idea: why not join the two cake in the network?

(Sm.shemu)

- Cut here -----------------------------------------------

------ Postings v1.0

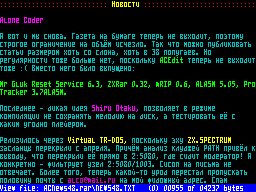

SCHEME

(AY-3-8910 / YM2149F)

ZX # 1 ZX # 2

GND GND

AY / 6 [1 k] AY/14

AY/14 [1 k] AY / 6

GND should be connected tightly. Thus it is necessary to check

the tester, unleashed a power supply components to the network

(to be isolated, but then ...) If GND is not connected tightly,

in violation of the contact may appear very large sparks -

until the fireballs;)

Kiloomy in the data prevent AY, in case they both would be

configured to output on the same line.

-------------------------------------------------- here ----

cut -

(This is an imitation of TAPE, which I unfortunately do not, by

AY'kov. Then try and printer port)

Used for the exchange of the 7 th bits of port A and B AY'ka.

Under the agreement, which I made with myself, port A (case 14)

works as an output, and port B (case 15) - to enter. Passive

state line, we assume logic 1 ("Termination")

Thus, the work will be tricky.

Initialization: in the register 14 is written AY # ff, and in

case 7 - # 40 (preferably in that order - then the state line

is not will vary).

After the game cycle comp # 1 (MASTER) set at its

A logic 0 port and waits for an appropriate response from the

company # 2 (SLAVE). When the PC # 2 deigns to put logic 0, the

exchange begins. The first transfers MASTER, SLAVE then

transmits a MASTER takes. Synchronous transfer option (first

experiments were not synchronized) is based on the fact that

the receiving subscriber forms meander, on every front by the

transmitting side puts in data line next bit. The first bit

appears at the positive differential. During the reception, the

last bit of the receiver gives even a positive difference by

which the transmitter sends its line of data in the state of

logic 0 and itself becomes the receiver. After a similar

exchange in the opposite direction the session ends. Both

computers translate the line into a state of logic 1.

Interrupt handler has a command RET. The maximum that has

there can afford - it is some increment. Main

the first stage - simply record the fact that the interruption

was. We assume that such termination, together with the capture

is performed for 25 cycles.

send: receive:

... ...

LD B, C LD B, C

OUT (C), E; 15 OUT (C), E; 15

DEC E DEC E

RLC (HL) IN A, (C)

SBC A, A OUT (C), E; 14

INF LD B, D

JP P / M, $ -2 OUT (C), C / E

OUT (C), E; 14 INC E

LD B, D RLA

OUT (C), A RL (HL)

INC E

... ...

The delay is calculated as follows.

In the most pessimistic case, the transmitter has undergone an

interrupt receiver interrupt is not received, and the front at

which to was to change the data transmitter failed was taken

immediately after the command INF. Then, the reaction time to

the front (before commands OUT (C), A, including) 60 25 clock

cycles, assuming the interrupt. In turn, from the moment of

this before the next front must pass 28 cycles, otherwise the

receiver would take the wrong information.

Further, in the heart again, worst case, assume that the

receiver works 2 times faster than the transmitter, while its

edges are rotate through at least (60 +25) · 2 28 = 198 cycles.

Hence it follows that should be 198-83 = 116 beats.

Understand?

Now this protocol exchanges Wolf 3D Deathmatch Arena

Tournament 2003:)

The annex should be based on the source asynchronous (speed of

the computer should not differ by more than 5%) - The Game

"Shoot the square". One computer calls the MASTER, and the

other - SLAVE. Autodetection yet!

Other articles:

News - scheme of concurrent interface AY. |

Thoughts - Crank pay any 1000r of redesigning STS by Scorpion. |

ACEdit - A list of honored Neispolzovateley AC Edit. |

Similar articles:

В этот день... 8 May