|

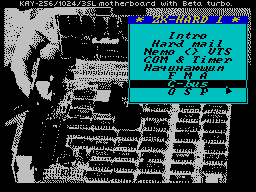

ZX Hard #00

31 августа 1998 |

|

subtleties of working with IORQGE / - what kind of signal and what it all eaten.

Subtleties of working with IORQGE /

(C) VTS'98

In ZF'8 Nemo in the description of a new KAY'a mentioned that

the formation of IORQGE only need to use the port address.

Because Accordingly, I personally encountered, I decided

Tell me more, because mostly

mentioned (and does!) that need to form this signal in fact the

choice of port.

To begin with I was a little step back and tell

for those who do not know what the signal is and what it all

eaten.

This signalets appears in the old

good Sinclair ZX-Spectrum ...

First of all, I note that he has a very

distant from the port # FF appointment (this

only a special case in the Scorpion). In addition, he is one of

the key moments in the architecture of ZX-Spectrum, because

gives opportunity to use part-time decoding of I / O ports,

inherent More Clive Sinclair and groaning as in the

ZX-revue, not quite relevant in this

issue of trafficking (see, for example, laudatory articles

Scorpio ('kutsee # FD', 'throw a couple LL'ok'...)). All

problems arose from the coders, and the iron is always

should be as simple as possible (in the manual / specification

/ standard). K example, in the entire address KAY'e

space occupied ports without payment

all ports # FF. A signal IORQGE can do so full decoding, as far

as is necessary in each case.

In addition, the corporate version of the ZX and KAY

below 1.5 point of interception was implemented on the

resistor, allowing you to work with the ports board

peripherals, although it is virtually meaningless. Especially

in the new KAY'e such a possibility already no.

Work with IORQGE / you must use

element with the MA (common emitter) or its

Emulation - trehstabilnoy logic or the diode (ie, active state

- ban - press the line to +5 v, otherwise - is free).

/ +5 V |>

\> E |> |

ban ban / ban

LP8

IOGE /

Make IORQGE / too easy. If you're going to have only one such

signal (And in future buy a PC with a bus), then

better make it to the resistor or diode. In KAY 1.5 it is

implemented on a chain LL1 elements (each slot).

IORQ / IORQGE /

IORQ/_Z80 IORQ / _motherboard

470

or so:

IORQ / IORQGE /

IORQ/_Z80 |> | o IORQ / _motherboard

4k7

(The latter is more reliable, especially when

on IORQ processor sitting a lot

155 or 531 series, and he himself did not IORQGE

restarted. However, this scheme can not be

use chain (0.7v on the diode)).

Well, now own about because of what

all this fuss is about. I mean, where in general

it (IORQGE /) to take? And why is there all

alarmed?

Explain. I mean I sit and catch non-existent bug in a piece of

iron on 'Airplane'. And it does not spoymayu ;-)

And suddenly dawns on me.

And the problem is that the port I had

# F8 hex,% 1111 1000 bin and I flew straight to the favorite;)

# xxFD hex ... And gave the whole thing BORDER ... Ie kogda I

drew up IOGE / 'as the saying goes anywhere': IORQ /, WR /,

ADR, he did not keep up with nimble IORQ, which managed to

smuggle in 'needle' on the board and front (you can decline) to

write data to same nimble 1533 registers.

Even greater horror I felt when I saw

(In the manual for the Z80), which appears just before IORQ

address. But then I thought (Not at once;)) that there is

nothing terrible - think of it, blocking ports

when the address in memory;).

Although there may still need to identify the WR / RD. And it

can be done Only with the advent of IORQ ...

If you block ports and write, and

reading, must be used when forming IORQ address only.

If you block only records will have

dodge. Namely: Shaping IORQGE /

on arrival address. Then we wait until

WR / RD and already locked IORQ. If

it appears that reads, IORQGE /

shoot. The result is a delay

IORQ card at ten nanoseconds

nestrashno that too, because he is sooo

dlinnyuyuyuyuschy (neturbirovanny).

If you lock a read-only do the same, but remove IORQGE on

arrival WR

Here, however, one could argue: it reads the processor will

wait for another 2 cycles already, why fuss for nothing? May it

is so, but the conflict on the data bus - thing is not so

desirable. Especially when you consider all sorts of left-wing

components and an increase in delays during buffering, bus ...

(Ie, increasing the duration of the conflict)

21.08.98 22:53 msk is-dos

Other articles:

Similar articles:

В этот день... 24 March