МИКРОПРОЦЕССОР Z80

СИСТЕМА КОМАНД

Помимо 78 команд своего предшественника — микропроцессора I8080, в Z80 реализовано 80 но-

вых. В целом он обрабатывает 696 кодов операций (с учетом использования в командах различных

регистров, способов адресации и т. п.).

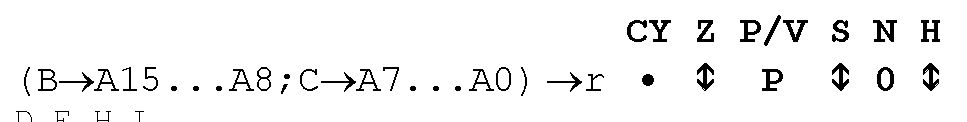

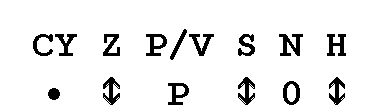

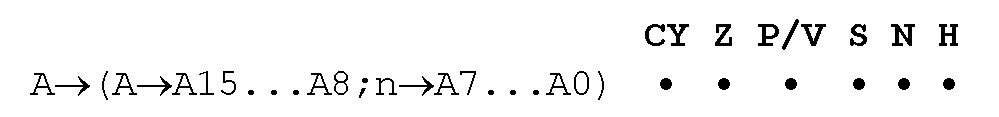

Для каждой команды приведено мнемоническое обозначение на языке ассемблера, схема, пояс-

няющая ее работу, и состояние флагового регистра после выполнения команды.

При записи команд приняты следующие обозначения:

А — 8-разрядный регистр аккумулятора;

В,С^,Е,Н^ — 8-разрядные регистры данных;

I — 8-разрядный регистр вектора прерываний;

R — 8-разрядный регистр регенерации динамического ОЗУ;

AF — 1 6-разрядный регистр, старший байт которого содержит значение аккумулятора, а млад-

ший байт — значение флагового регистра;

ВС,DE,HL — 16-разрядные спаренные регистры;

IX,IY — 16-разрядные индексные регистры;

SP — 16-разрядный регистр указателя стека;

PC — 16-разрядный регистр счетчика команд;

n — 8-разрядный операнд, непосредственно указанный в команде;

nn — 16-разрядный операнд, непосредственно указанный в команде;

(HL),(ВС),(DE) — 8-разрядные значения ячеек памяти, адреса которых содержатся в соответст-

вующих регистровых парах;

(nn) — в командах, оперирующих байтами:

8-разрядное значение ячейки памяти, адрес которой задается двумя байтами nn непосредст-

венно в команде;

(nn) — в командах, оперирующих 16-разрядными значениями:

Имя символьного массива может состоять только из одной буквы. Его элементы хранятся в та-

ком же порядке, что и элементы численного массива.

При определении массива оператором Бейсика DIM всем его элементам присваивается значение

32 (#20) — код символа «пробел».

16-разрядное значение смежных ячеек памяти, адрес nn первой из которых (младшего байта

значения) указан непосредственно в команде, адрес второй ячейки (старшего байта значения)

равен пп+1;

(IX+d), (IY+d) — 8-разрядные значения ячеек памяти, адреса которых вычисляются сложением

значения соответствующего индексного регистра и 8-разрядного смещения d, указанного непо-

средственно в команде;

b — номер участвующего в операции бита (0...7);

cc — условие, при истинности которого выполняется команда;

е — 8-разрядное смещение относительно текущего адреса;

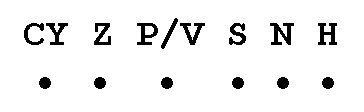

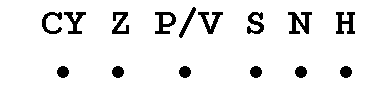

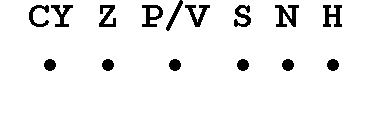

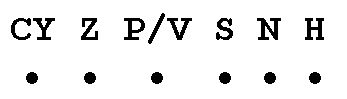

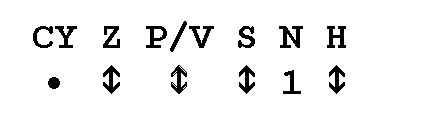

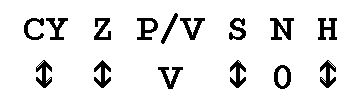

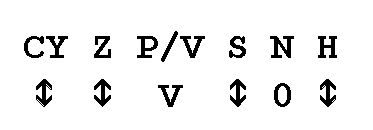

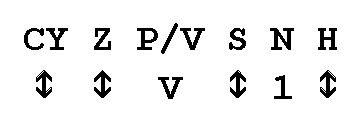

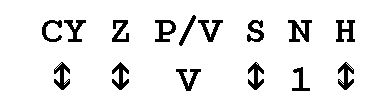

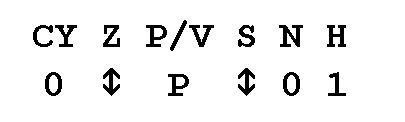

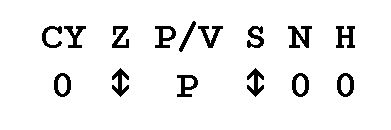

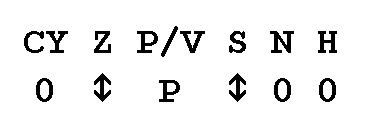

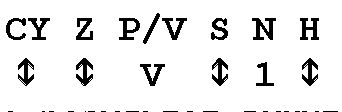

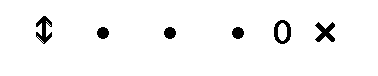

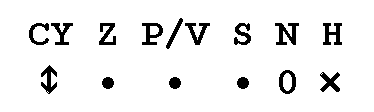

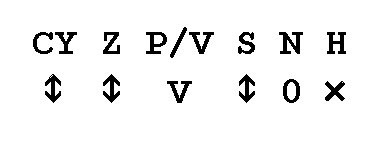

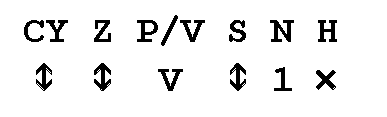

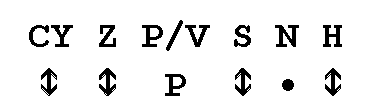

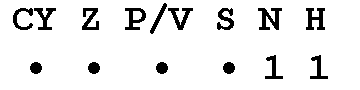

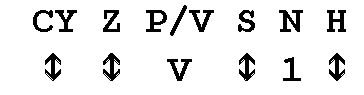

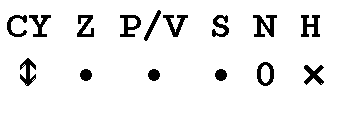

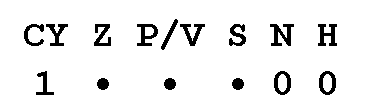

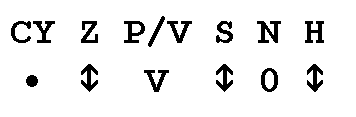

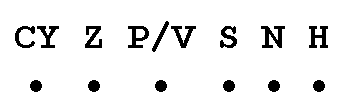

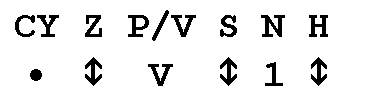

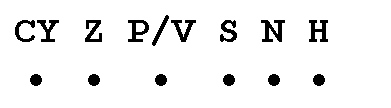

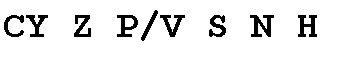

CY — значение флага переноса;

$ — состояние флага изменяется в результате операции;

• — состояние флага не изменяется в результате операции;

0 — флаг сбрасывается в результате операции;

1 — флаг устанавливается в результате операции;

X — состояние флага не определено;

V — флаг P/V индицирует арифметическое переполнение в результате операции;

Р — флаг P/V индицирует «четность» в результате операции.

Операнд, из которого берется значение для выполнения операции, называется источником, а

операнд, в который помещается результат — приемником. В мнемониках команд, использующих два

операнда, первым, как правило, записывается приемник, затем, через запятую, — источник. В

процессе выполнения команды содержимое источника не меняется. Если команда содержит один

операнд, то он одновременно может быть и источником, и приемником.

МЕТОДЫ АДРЕСАЦИИ

После описания каждого метода адресации приведено по два примера его использования.

Безоперандные команды. Для их выполнения процессору не требуется дополнительных значений:

HALT

NOP

Регистровая адресация. Операнд содержится в регистре, который непосредственно указан в ко-

манде:

INC A

ADD HL,BC

Непосредственная адресация. Операнд расположен в ячейке памяти, непосредственно следующей

за кодом команды. Если операнд двухбайтовый, то он занимает две ячейки за кодом команды

(расширенная непосредственная адресация):

LD С,%1011

LD HL,#1234

Неявная адресация. Регистр, в котором содержится операнд, однозначно определен данной ко-

мандой:

RLA

LDIR

Регистровая косвенная адресация. Операнд расположен в ячейке памяти, адрес которой содер-

жится в регистровой паре:

DEC (HL)

LD А,(ВС)

Далее по тексту для обозначения этого типа адресации будет использоваться фраза: «операнд

расположен в ячейке, адресуемой регистром».

Индексная адресация. Адрес размещения в памяти операнда образуется сложением значения ин-

дексного регистра и некоторого смещения (—128...+127), явно указанного в команде:

SLA (IX+2)

LD A,(IY-25)

Косвенная адресация. Адрес операнда содержится в ячейках памяти, расположенных непосредст-

венно за кодом команды:

LD А,(1234)

LD (#C000),DE

Побитовая адресация. Командой задается конкретный бит операнда, над которым будет прово-

диться операция:

SET 4,(HL)

BIT 7,A

Относительная адресация. Адрес задается как однобайтовое смещение (-128...+ 127) относи-

тельно текущего значения регистра счетчика команд*:

JR $+#23

DJNZ $-6

Расширенная адресация. Адрес задается двухбайтовым операндом:

CALL 1234

JP NC,#1601

Различные методы адресации могут быть совмещены в командах, работающих с двумя операндами:

LD (HL),12

КОМАНДЫ Z80

Команды пересылок

LD r, s s ^ r

где r - А,В,С^,Е,Н,^

s - А,В,С^, E^L или n,(HL),(IX+d),(IY+d).

LD d,r r ^ d

где r — А,В, ^DjE^L или n;

d - A,B,C,D,E,H,L или (HL),(IX+d),(IY+d).

*) Необходимо учитывать, что код смещения, содержащийся в коде команды и записанный в тексте ассемблера, бу-

дет различным. Ассемблер отсчитывает смещения относительно счетчика адресов $, хранящего адрес команды, тогда

как микропроцессор использует содержимое регистра PC, увеличивающееся каждый раз при выборе очередного байта

команды из памяти.

LD A,s s ^ A

LD d,A A ^ d

где s и d - (BC),(DE) или (nn).

LD A,s s ^ A

LD d,A A ^ d

где s и d — I или R.

Пересылка байта из источника в приемник без изменений. Содержимое флагового регистра F не

меняется. Исключение составляют команды LD А,1 и LD A,R, которые отображают состояние триггера

разрешения прерываний в бите четности/переполнения P/V регистра флагов.

LD dd,nn nn ^ dd

LD dd,(nn) (nn) ^ dd

где dd - BC,DE,HL,SP,IX,IY.

LD (nn),ss ss ^ (nn)

где ss - BC,DE,HL,SP,IX,IY.

LD SP,ss ss ^ SP

где ss - HL,IX или IY.

Пересылка двух байтов из источника в приемник без изменений.

PUSH ss SP - 2 ^ SP;ss ^ (SP)

где ss - BC,DF,HL,AF,IX,IY.

Запись содержимого регистра в стек. Значение указателя стека уменьшается на 2.

POP ss (SP) ^ ss;SP+2 ^ SP

где ss - BC,DE,HL,AF,IX,IY.

Запись значения из стека в регистр. Значение указателя стека увеличивается на 2.

Команды информационного обмена

ЕХ DE, HL DE ^ HL

Обмен содержимого регистров. В DE помещается содержимое HL, а в HL — содержимое DE.

ЕХ (SP),ss (SP) ^ss

где ss - HL,IX,IY.

Обмен со стеком. Значение вершины стека меняется местами с содержимым регистра ss (значение указателя

стека не изменяется).

Команды переключения набора регистров

ЕХ AF,AF' AF О- AF'

Переключение регистров А и F на альтернативные. После выполнения этой команды все действия будут осу-

ществляться над альтернативными регистрами А' и F'. Возвратиться к основному набору можно, повторно вы-

полнив команду ЕХ AF.AF'. Процессор не фиксирует, какой из двух наборов активен в данный момент.

EXX DE О- DE';HL О- т^ВС О- ВС'

Переключения активного набора регистров. Если ранее активным являлся основной набор (HL, DE, ВС), то после

выполнения команды — альтернативный (HL', DE', ВС'), и наоборот. Команда аналогична команде ЕХ AF,AF' .

Команды пересылки блока и команды поиска

LDI (HL) ^ (DE)

HL+1 ^ HL; DE+1 ^ DE

ВС-1 ^ ВС

Пересылка содержимого ячейки памяти с инкрементом. Байт из ячейки, адресуемой регистром HL, пересыла-

ется в ячейку, адресуемую регистром DE, содержимое регистров HL и DE увеличивается на единицу, а регист-

ра ВС уменьшается на единицу. Если в результате выполнения команды ВС=0, то флаг P/V сбрасывается, в

противном случае P/V=1.

LDIR

Пересылка блока памяти с инкрементом. Действие аналогично команде LDI, только пересылается группа

байт, расположенных в сторону увеличения адресов от ячейки, адресуемой регистром HL. Количество переда-

ваемых байт определяется регистром ВС. Аналогичного результата можно добиться, выполнив фрагмент про-

граммы:

LOOP LDI

JP PE,LOOP

LDD

Пересылка содержимого ячейки памяти с декрементом. Байт из ячейки, адресуемой регистром HL, пересыла-

ется в ячейку, адресуемую регистром DE, содержимое регистров HL, DE и ВС уменьшается на единицу. Если в

результате выполнения команды ВС=0, то флаг P/V сбрасывается, в противном случае P/V=1.

LDDR

Пересылка блока памят

байт, расположенных в ст

ваемых байт определяется

граммы:

LOOP LDD

JP PE,LOOP

СPI A-HL

HL+1 ^ HL

ВС-1 ^ ВС

Сравнение значения аккумулятора с содержимым ячейки памяти с инкрементом. Ячейка памяти адресуется HL. Если

A=(HL), устанавливается флаг Z, в противном случае Z=0. После сравнения содержимое регистра HL увеличивается на

единицу, а ВС на единицу уменьшается. Если в результате выполнения команды ВС=0, то флаг P/V сбрасывается, в

противном случае P/V=1.

CPIR

Поиск значения аккумулятора в блоке памяти с инкрементом. Начальный адрес блока задается регистром HL,

длина — регистром ВС. Поиск производится в сторону увеличения адресов. При совпадении значения аккумуля-

тора с содержимым ячейки памяти устанавливается флаг Z (если байт не найден — Z=0), регистр HL будет со-

держать адрес последующей ячейки в блоке, а ВС — ее обратный порядковый номер.

CPDR

Поиск значения аккумулятора в блоке памяти с декрементом. Конечный адрес блока задается в регистре HL,

длина — в регистре ВС. Поиск производится в сторону уменьшения адресов. При совпадении значения аккуму-

лятора с содержимым ячейки памяти устанавливается флаг Z(если байт не найден — Z=0), регистр HL будет

содержать адрес предыдущей ячейки в блоке, а ВС — ее порядковый номер.

Команды бинарных операций

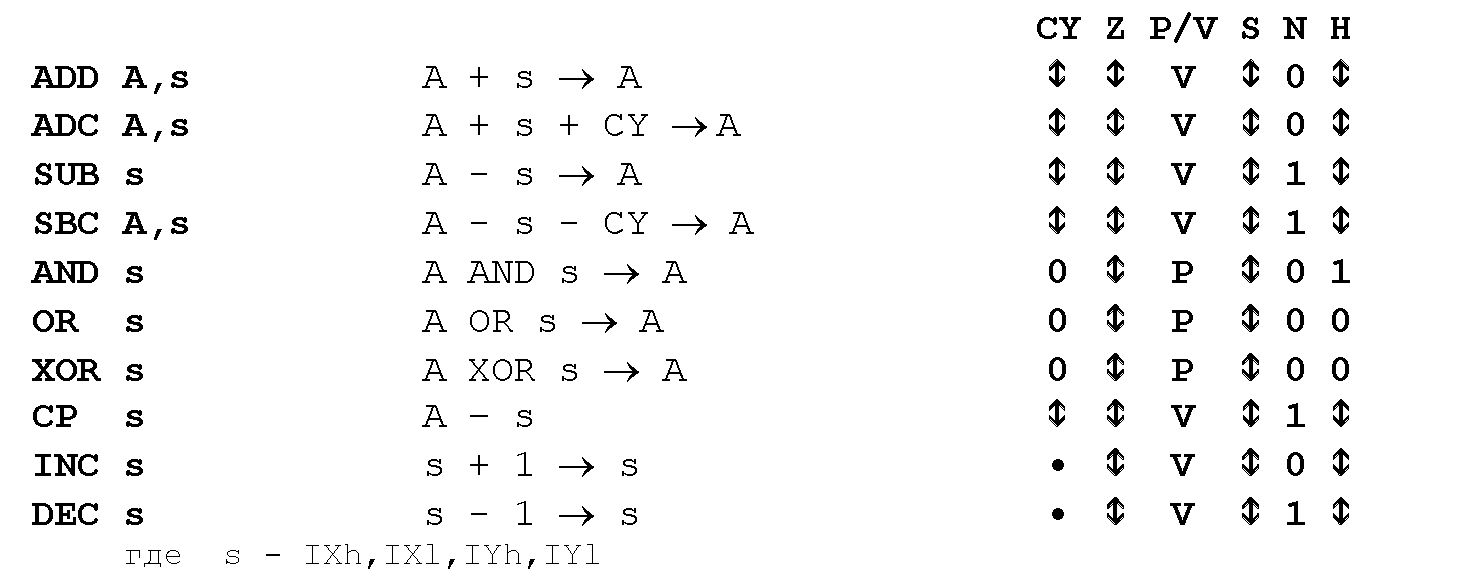

Арифметическиe и логическиe операции над 8-разрядными операндами

В качестве приемника в этой группе команд всегда служит аккумулятор, а символом s обозна-

чены операнды — а,в,с^,е,н^,п, (HL), (IX+d), (IY+d).

ADD A,s А + s ^ A

Арифметическое сложение.

ADC A,s A + s + CY ^ A

Арифметическое сложение с переносом.

SUB s A - s ^ A

Арифметическое вычитание.

SBC A,s A - s - CY ^ A

Арифметическое вычитание с переносом.

AND s A AND s ^ A

Поразрядное логическое «И».

OR s A OR s ^ A

Поразрядное логическое «ИЛИ».

XOR s A XOR s ^А

Поразрядное исключающее «ИЛИ».

CP s A - s

Сравнение. Выполняется аналогично команде SUB s, но результат вычитания не записывается, а только в

соответствии с ним изменяются биты флагового регистра.

В табл. 6 приведены состояния флагов, соответствующие результатам сравнения, а также мне-

моники условий, при выполнении которых будет осуществляться переход в командах условного пе

рехода.

Таблица 6. Результаты сравнения операндов.

Арифметические и логические действия над 16-разрядными операндами

CPD А-(HL)

Сравнение значения

содержимым ячейки

Ячейка памяти

HL. Если A=(HL),

в противном случае Z=0

значения регистров HL

единицу. Если в

команды ВС=0, то флаг

противном случае P/V=1

ADD HL, ss HL + ss ^ HL

где ss - ВС,DE,HL,SP.

ADD IX,ss IX + ss ^ IX

где ss - ВС,DE,IX,SP

ADC HL,ss HL + ss + CY ^ HL

где ss - BC,DE,HL,SP.

Арифметическое сложение с переносом.

SBC HL,ss HL - ss - CY ^ HL

где ss - BC,DE,HL,SP.

Арифметическое вычитание с переносом.

Команды унарных операций

В трех следующих командах преобразования производятся над числом, записанным в аккумуля-

тор.

DAA BCD (A) ^ A

Преобразование числа в упакованный двоично-десятичный формат. Используется обычно после операций над

двоично-десятичными числами*.

Пусть, например, нужно сложить два двоично-десятичных числа 15 и 39 (00010101 и 00111001

соответственно).

LD А, %00010101

LD С,%00111001

ADD A, C ;А=%01001110

DAA ;А=%01010100

Согласно правилам двоичной арифметики в результате сложения в аккумулятор будет помещено

число #4Е, однако операция DAA скорректирует это значение, и конечный результат составит 54.

CPL А ^ А

Преобразование числа в обратный код (все биты инвертируются).

NEG 0 — A ^ A

Преобразование числа в дополнительный код.

CCF CY ^ CY

Инвертирование значения флага переноса CY.

SCF 1 ^ CY

Установка флага переноса CY.

INC d d + 1 ^ d

где d - А,В,С,В,Е,И,Ь,(ИЬ),(IX+d),(IY+d).

INC dd dd + 1 ^ dd

где dd - BC,DE,HL,SP,IX,IY.

Инкремент (прибавление к значению операнда единицы).

DEC d d - 1 ^ d

где d - A,B,C,D,E,H,L,(HL),(IX+d),(IY+d).

DEC dd dd - 1 ^ dd

где dd - BC,DE,HL,SP,IX,IY.

Декремент (вычитание из значения операнда единицы).

*) В двоично-десятичных числах цифры от 0 до 9 кодируются четырьмя битами, причем комбинации 1010...1111 не исполь-

зуются. Таким образом в одном байте может быть записано только две цифры. Это расточительно с точки зрения экономии па-

мяти, но гарантирует отсутствие ошибки «машинного» округления.

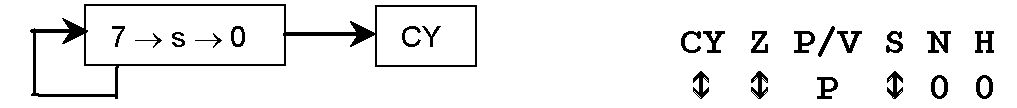

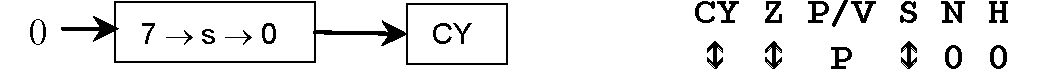

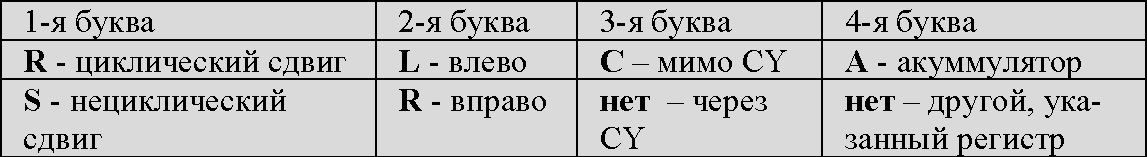

Команды сдвига

В следующих четырех командах операция сдвига осуществляется над числом, записанным в акку-

мулятор.

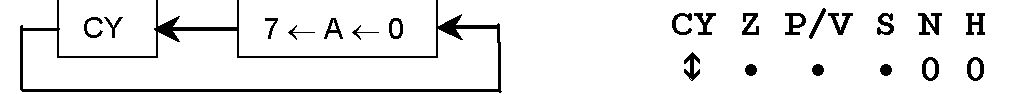

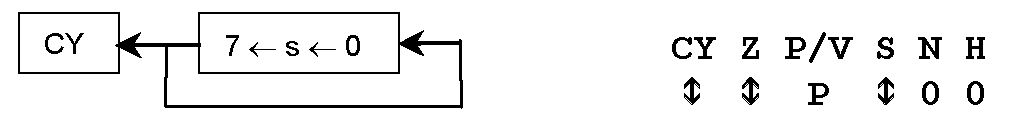

RLCA

Циклический сдвиг влево на один разряд, значение старшего бита записывается во флаг переноса CY.

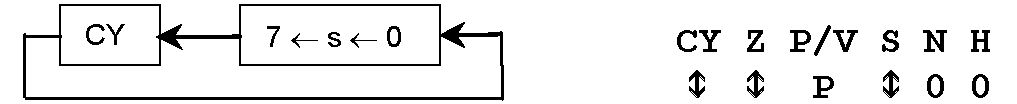

RLA

Циклический сдвиг влево через флаг переноса CY

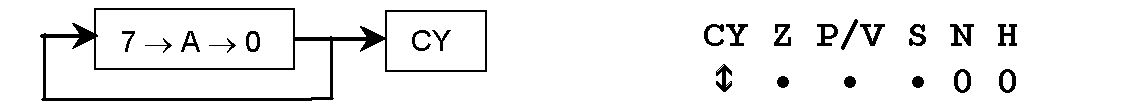

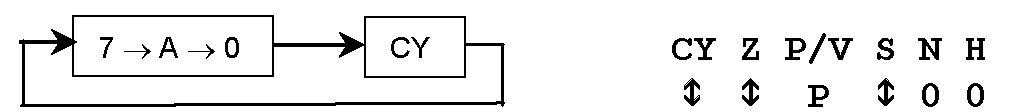

RRCA

Циклический сдвиг вправо на один разряд, значение младшего бита записывается во флаг переноса CY

RRA

Циклический сдвиг вправо через флаг переноса CY.

В следующих семи командах операция сдвига осуществляется над числом, записанным в одном из

операндов — А^^^^^^, (HL),(IX+d),(IY+d), обозначенных символом s.

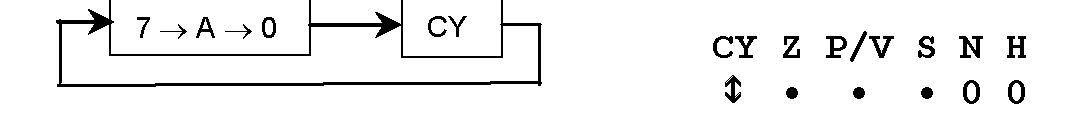

RLC s

Циклический сдвиг влево на один разряд, значение старшего бита записывается во флаг переноса CY.

RL s

Циклический сдвиг влево через флаг переноса CY

RR s

Циклический сдвиг вправо через флаг переноса CY.

RRC s

Циклический сдвиг вправо на один разряд, значение младшего бита записывается во флаг переноса CY.

SLA s

ЗДвиг влево на один разряд, в младший бит записывается 0, старший бит переписывается во флаг переноса

CY (умножение на 2).

SRA s

Сдвиг вправо на один разряд, содержимое старшего бита не изменяется, младший бит переписывается во флаг пере-

носа CY (деление на 2 со знаком).

SRL s

ЗДвиг вправо на один разряд, в старший бит записывается 0, младший бит переписывается,во флаг переноса

CY (деление на 2).

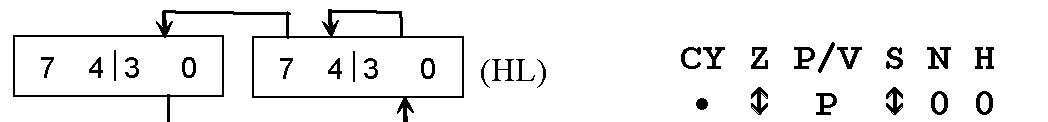

Команды циклического переноса

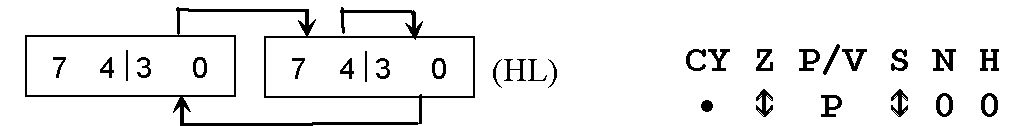

RLD

Левый арифметический циклический перенос тетрады из аккумулятора в ячейку памяти, адресуемую регистром HL.

Старшая тетрада (биты 7... 4) ячейки памяти переносится в младшую тетраду аккумулятора (биты 3...0), младшая

тетраде аккумулятора переносится в младшую тетраду ячейки памяти, а младшая тетрада ячейки памяти — в старшую

тетраду ячейки памятт/г

RRD

Правый арифметический циклический перенос тетрады из аккумулятора в ячейку памяти, адресуемую регист-

ром HL. Старшая тетрада (биты 7...4) ячейки памяти переносится в младшую (биты 3...0), младшая тетрада

ячейки памяти переносится в младшую тетраду аккумулятора, а младшая тетрада аккумулятора — в старшую

тетраду ячейки памяти.

Команды операций над отдельными битами

BIT b,d db ^ Z

где d - A,B,C,D,E,H,L,(HL),(IX+d),(IY+d).

Проверка состояния бита, номер которого задается числом Ь в пределах от 0 (младший) до 7 (старший).

Результат проверки помещается в бит Z регистра флагов (если проверяемый бит равен нулю, то Z=l).

SET b,d 1 ^ db

где d - А,В,С,D,E,И,Ь,(ИЬ),(IX+d),(IY+d).

Установка бита. В бит с номером Ь записывается единица.

RES b,d 0 ^ db

где d - А^^^^,^^^^ , (IX+d ), (IY+d).

Сброс бита. В бит с номером Ь записывается ноль.

Команды управления процессором

NOP

Нет операции. Регистры и флаги не изменяются (за исключением регистров PC и R), процессор переходит ]

ыполнению следующей за NOP команды.

HALT

Останов процессора. Выполнение команды HALT эквивалентно бесконечному выполнению команды NOP, но без

изменения значения регистра счетчика команд PC. Выход из состояния останова происходит либо при аппарат-

ном сбросе процессора, либо с приходом сигнала маскируемого или немаскируемого прерывания. После выпол-

нения программы обработки прерывания, управление будет передано на ячейку, следующую за командой HALT.

В ZX Spectrum команда HALT обычно используется для синхронизации выполнения программы от-

носительно полукадровых прерываний, происходящих каждые 1 /50 секунды.

DI 0 ^ IFF1;0 ^ IFF2

Запрет маскируемых прерываний*. Сбрасывается триггер разрешения прерываний IFF.

EI 1 ^ IFF1;1 ^ IFF2

Разрешение маскируемых прерываний. Устанавливается триггер разрешения прерываний IFF.**

IM 0

IM 1

IM 2

Установка режима обработки маскируемых прерываний. Устанавливаются, соответственно, режимы О, 1 или

2.

Команды для работы с подпрограммами

CALL nn SP-2^SP;PC^(SP);nn^-PC©

Безусловный переход к подпрограмме, расположенной по адресу nn, адрес следующей за CALL команды запи-

сывается в стек.

CALL cc,nn SP-2^SP;PC^ (SP);nn^PC©

(при выполнении условия сс)

где сс — NZ — не ноль (флаг 2=0);

Z — ноль (флаг Z=1);

NC — нет переноса (флаг CY=0);

С — перенос (флаг CY=1);

PO — нечетность (флаг P/V=0);

РЕ - четность (флаг P/V=1);

Р — положительное (флаг S=0);

М — отрицательное (флаг S=1).

Условный переход к подпрограмме, расположенной по адресу nn. Переход осуществляется при выполнении условия

:c, в противном случае команда игнорируется и управление передается следующей команде программы._

©На самом деле сначала выполняется nn^-PC а затем всё остальное, что я обнаружил при взломе одной иг-

)ушки.

*)Более подробно о командах, обслуживающих прерывания, см. «Архитектура ZX Spectrum».

**)Следует отметить, что при выполнении команды EI запрещаются маскируемые прерывания на время между

этой и следующей командами.

RET (SP) ^ PC;SP + 2 ^ SP

Безусловный возврат из подпрограммы. Управление передается команде, расположенной по адресу, извле-

каемому из стека.

RET cc (SP) ^ PC;SP + 2 ^ SP

(при выполнении условия cc)

где cc - NZ,Z, NC,C,PO, РЕ,Р,М (см. CALL cc,nn).

Условный возврат из подпрограммы. Возврат из подпрограммы происходит при выполнении условия cc, в

противном случае команда игнорируется.

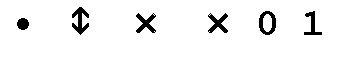

RETI IFF2^IFF1;(SP) ^PC;SP+2^SP

Возврат из маскируемого прерывания.

RETN IFF2^IFF1;(SP)^PC;SP+2^SP

Возврат из немаскируемого прерывания.

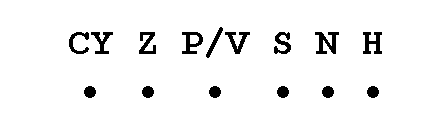

CY Z P/V S N H

• • • • • •

RST р SP-2^SP;PC^(SP);p^PC©

где р - 0,8,16,24,32,4 0,4 8 или 56.

Командное прерывание. Безусловный переход к подпрограмме, расположенной по фиксированному адресу р; выполня-

ется аналогично команде CALL p.

Команды условного и безусловного перехода

JP nn nn ^ PC

Безусловный переход по абсолютному адресу. Управление передается команде, расположенной по адресу nn.

JP cc,nn nn ^ PC

(при выполнении условия cc)

где cc - NZ,Z,NC,C,PO,РЕ,Р,М (см. CALL cc.nn).

Условный переход по абсолютному адресу. Передача управления происходит только при выполнении условия

c, в противном случае выполняется следующая команда программы.

JR e PC + е ^ PC

где е — смещение относительно текущего адреса.

Безусловный переход по относительному адресу. Управление передается команде, расположенной по адресу,

юлученному прибавлением смещения е к текущему значению счетчика команд.

JR cc,e PC + е ^ PC

(при выполнении условия ее)

где е — смещение относительно текущего адреса,

cc — NZ — не ноль (флаг Z=0);

Z — ноль (флаг Z=1);

NC — нет переноса (флаг CY=0);

С — перенос (флаг CY=1).

Условный переход по относительному адресу. Передача управления происходит только при выполнении усло-

вия cc, в противном случае выполняется следующая команда программы.

JP (ss) ss - PC

где ss - HL,IX или IY.

Безусловный переход по адресу, содержащемуся в регистре ss.

DJNZ е

Условный переход по относительному адресу при ненулевом счетчике.

Значение регистра В уменьшается на единицу. Если при этом B=/0, то осуществляется переход по адресу

РС+е , в противном случае управление передается следующей команде программы. Команда удобна для органи

зации циклов, счетчиком повторения в которых служит регистр В.

Команды ввода-вывода

IN A,(n)

где n — номер порта.

Ввод байта из порта и помещение его в аккумулятор. Полный 16-разрядный адрес порта составляется из

значения n (младший байт) и значения аккумулятора (старший байт).

IN г,(с)

где r - А,В,С,d,e,h,l.

Ввод байта из порта и помещение его в регистр. Адрес порта содержится в регистре ВС (в С — младший

байт адреса, В — старший). Далее вместо подобного словосочетания будет использоваться фраза «порт адре-

суется регистром ВС».

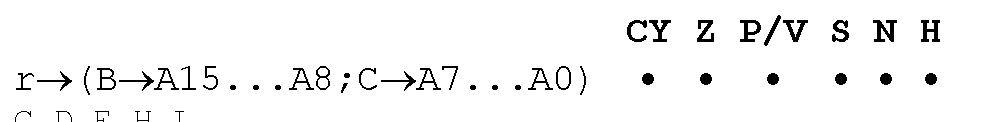

IN (HL), (C) F(E ^ Л15...Л8;С ^ А7...А0)

Ввод байта из порта с выставлением флагов. Адрес порта задается регистром ВС. Команда аналогична ко-

манде IN r,(C|, но при ее выполнении принятый байт никуда не записывается, а только в зависимости от его

значения изменяются биты флагового регистра.

INI

Ввод байта из порта в ячейку памяти с инкрементом. Байт считывается из порта, адресуемого регистром

ВС, и записывается в ячейку памяти, адресуемую регистром HL. После выполнения команды содержимое HL уве-

личивается на единицу, значение В на единицу уменьшается. Если в результате выполнения команды регистр В

обнуляется, то устанавливается флаг Z, в противном случае Z=0.

INIR

Ввод массива зна

ый адрес массива п.

ринимаемых байт ра:

диницу, HL увеличивается на единицу.

IND

Ввод байта из порта в ячейку памяти с декрементом. Байт считывается с порта, адресуемого регистром

ВС, и записывается в ячейку памяти, адресуемую регистром HL. После выполнения команды содержимое регист-

ров HL и В уменьшается на единицу. Если в результате выполнения команды В обнуляется, то устанавливается

флаг Z, в противном случае Z=0.

INDR

Ввод массива значений из портов в память с декрементом. Адреса портов задаются регистром ВС, началь-

ный адрес массива памяти — регистром HL. Ввод осуществляется в сторону уменьшения адресов, количество

принимаемых байт равняется значению регистра В. После приема очередного байта содержимое регистров В и

HL уменьшается на единицу.

OUT (n),A

где n — номер порта.

Вывод байта из аккумулятора в порт с номером п. Полный 16-разрядный адрес порта составляется из зна-

чения п (младший байт) и значения аккумулятора (старший байт).

OUT (C),r

где r - а,в,с^,е ,h,l.

Вывод байта из регистра г в порт, адресуемый регистром ВС (С — младший байт адреса, а В — старший).

OUTI

Вывод байта из ячейки памяти в порт с инкрементом. Байт считывается из ячейки памяти, адресуемой ре-

гистром HL, и пересылается в порт, адресуемый регистром ВС. После выполнения команды содержимое HL уве-

тачивается на единицу, значение В уменьшается на единицу. Если в результате выполнения команды регистр В

обнуляется, то устанавливается флаг Z, в противном случае Z=0.

OTIR

Вывод массива из памяти в порты с инкрементом. Адреса портов задаются регистром ВС, начальный адрес

массива — регистром HL. Вывод осуществляется в сторону увеличения адресов, количество передаваемых байт

равно значению регистра В. После передачи очередного байта содержимое регистра В уменьшается

на единицу, регистра HL увеличивается на единицу.

OUTD

Вывод байта из ячейки памяти в порт с декрементом. Байт считывается из ячейки памяти, адресуемой ре-

гистром HL, и пересылается в порт, адресуемый регистром ВС. После выполнения команды содержимое регист-

ров HL и В уменьшается на единицу. Если в результате выполнения команды В обнуляется, то устанавливается

флаг Z, в противном случае Z=0.

OTDR

Вывод массива из памяти в порты с декрементом. Адреса портов задаются регистром ВС, начальный адрес

массива — регистром HL. Вывод осуществляется в сторону уменьшения адресов, количество передаваемых байт

равно значению регистра В. После передачи очередного байта содержимое регистров В и HL уменьшается на

единицу.

Недокументированные команды

При использовании 8-разрядной шины данных непосредственно можно реализовать только 25 6 ко-

дов команд (28=256). Остальные 440 (696-256) кодов команд Z80 являются двухбайтными — первым

байтом кода в них стоит один из четырех префиксов: #СВ, #DD, #ED, #FD*. Следовательно, кроме

описанных 696 кодов команд возможно составить еще много вариантов «неучтенных» кодов. Выпол-

нение некоторых из них может привести к вполне осмысленным результатам. Эти коды составляют

так называемые недокументированные команды. В фирменных описаниях процессора эти команды не

приводятся, однако многие программисты пользуются ими: иногда для удобства, иногда из сооб-

ражений секретности (отладчики обычно «не берут» такие команды), иногда для позы, мол, по-

смотрите, какой я умный.

Чаще всего применяются недокументированные команды, работающие с частями индексных регист-

ров как с 8-разрядными регистрами общего назначения. Эти регистры, верней, части регистров

обозначаются IXh, 1X1 (старший и младший байты регистра IX) и IYh, IY1 (старший и младший

байты регистра IY).

Ниже приведены некоторые недокументированные команды Z8 0:

*)Байты #DD и #FD содержатся в кодах команд, работающих с индексными регистрами (IX и IY соответст-

венно); #СВ — в кодах команд, работающих с битами; #ED — в кодах остальных двухбайтных команд.

LD r,s s ^ r

где r - А,В,С,0,Е;

s - IXh,IXl,IYh,IYl.

LD d,r r ^ d

где r - А,В,С,В,Е или n;

d - IXh,IXl,IYh,IYl.

Этими командами удобно пользоваться, когда нужно загрузить индексный регистр из какого-

либо другого регистра. Например, вместо последовательности команд

PUSH DE ;запись в стеке содержимого регистра DE

POP IX ;загрузка регистра IX значением из стека

можно использовать

LD IXh,D

LD IXI,E

Хотя вторая последовательность команд занимает в памяти на один байт больше, время ее вы-

полнения меньше на 9 тактов процессора. Ниже приведены недокументированные команды, действие

которых не отличается от действия «нормальных» команд байтовой арифметики.

Например, для увеличения значения регистра IX на 25 6 можно использовать недокументирован-

ную команду INC IXh, выполнение которой эквивалентно работе целой программы:

PUSH DE ;сохранение содержимого регистра DE

LD DE,256 ;загрузка регистра DE значением 256

ADD IX,DE ;увеличение содержимого регистра IX

POP DE ;восстановление значения регистра DE

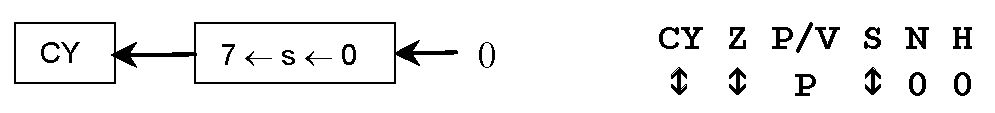

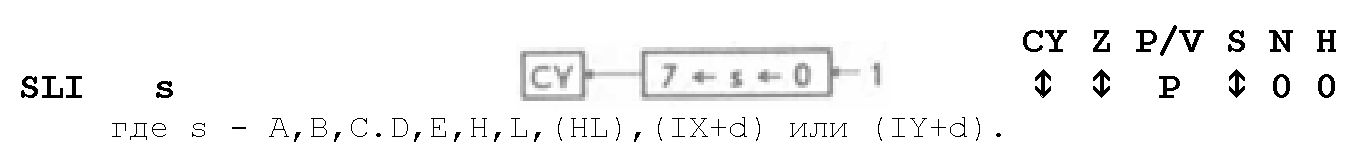

Приведем еще одну недокументированную команду, дополняющую группу команд сдвига:

Сдвиг содержимого регистра s влево на один разряд, в младший бит записывается 1, старший бит перепи-

сывается во флаг переноса CY.

Мы привели лишь несколько недокументированных команд микропроцессора Z8 0, надеемся, что

они будут Вам полезны. Если же Вас заинтересовали неизвестные возможности Z80, ничто не ме-

шает Вам поэкспериментировать самим.