1. Краткая характеристика

микропроцессора Z80

МП Z80 представляет собой БИС с 8500 транзисторами на Кристаллической пластине

площадью 4,6*4,9 мм2 и выпускается в DIP корпусе с 40 выводами. БИС выполнена по n-

канальной МОП технологии с кремниевыми затворами и работает от одного источника питания

+5В. Все входы и выходы микросхемы ТТЛ-совместимы

МП Z80 предназначен для работы с памятью (постоянной и оперативной) с общей

емкостью до 64К Память имеет байтовую структуру - возможна адресация в памяти любого байта.

Ширина выборки из памяти - 1 байт. При обращении к памяти используются 16-разрядные

(двухбайтные) адреса.

Организация МП Z80 отмечена следующими основными особенностями:

•S трехшинной структурой с шинами адреса, данных и управления;

•S наличием регистровой памяти, образованной программно доступными и общими и

специализированными регистрами, а также регистрами временного хранения;

•S наличием двух (главного и вспомогательного) аккумуляторов. Флаговых регистров и

наборов РОН;

•S магнетральным принципом связей, реализованным в виде связывающей основные узлы

МП двунаправленной шины данных, имеющей ширину, равную длине слов, обрабатываемых

микропроцессором (8 разрядов);

•S наличием 16-разрядной шины адреса, обеспечивавшей возможность прямой адресации

любого байта в памяти ёмкостью 64 Кбайт;

•S наличием 10 способов адресации: непосредственная, регистровая, косвенная,

абсолютная, модифицированная нуль-страничная, относительная, индексная, битовая, встроенная

и смешимая;

•S расширенным набором команд (158 базовых команд для работы с 16-, 8-, 4- и

однобитными данными);

•S наличием четырёх форматов команд (1-, 2-, 3- и 4-байтного);

•S наличием средств для работы с подпрограммами: команды вызова и возврата, с тон

числе условного;

•S наличием средств организации стековой памяти (регистр - указатель стека, схемы

дополнении операций инкремента декремента, специальные команды стековых операций);

•S наличием эффективных средств обработки массивов данных: пересылки, сравнения и

ввода/вывода блоков;

•S развитой системой прерываний: возможна реализация векторных многоуровневых

приоритетных прерываний без подключения БИС контроллера прерываний. Имеются 3

программно выбираемых режима маскируемого прерывания, а также немаскируемое прерывание;

•S возможностью реализации в МП режима прямого доступа к памяти путем подключения

специальной БИС (контроллера ПДП);

•S упроченными схемами интерфейса - отпадает необходимость в дополнительных БИС,

таких как, например, генератор тактовых импульсов и системный контроллер для МП I8080;

•S наличием встроенной схемы регенерации динамического ОЗУ.

Программное обеспечение МП совместимо с программной частью МП Intel 8080 Набор

команд Z80, по существу, является расширенным набором команд I8080, поэтому МП Z80 может

выполнять программы, написанные для I8080.

Архитектуре МП Z80 является типичной для 8-разрядных микропроцессоров. В ней можно

выделить следующие основные части:

•S блок регистров,

•S арифметическо-логическое устройство,

•S регистр команд,

•S дешифратор команд и устройство управления,

•S схемы управления шинами адреса и данных.

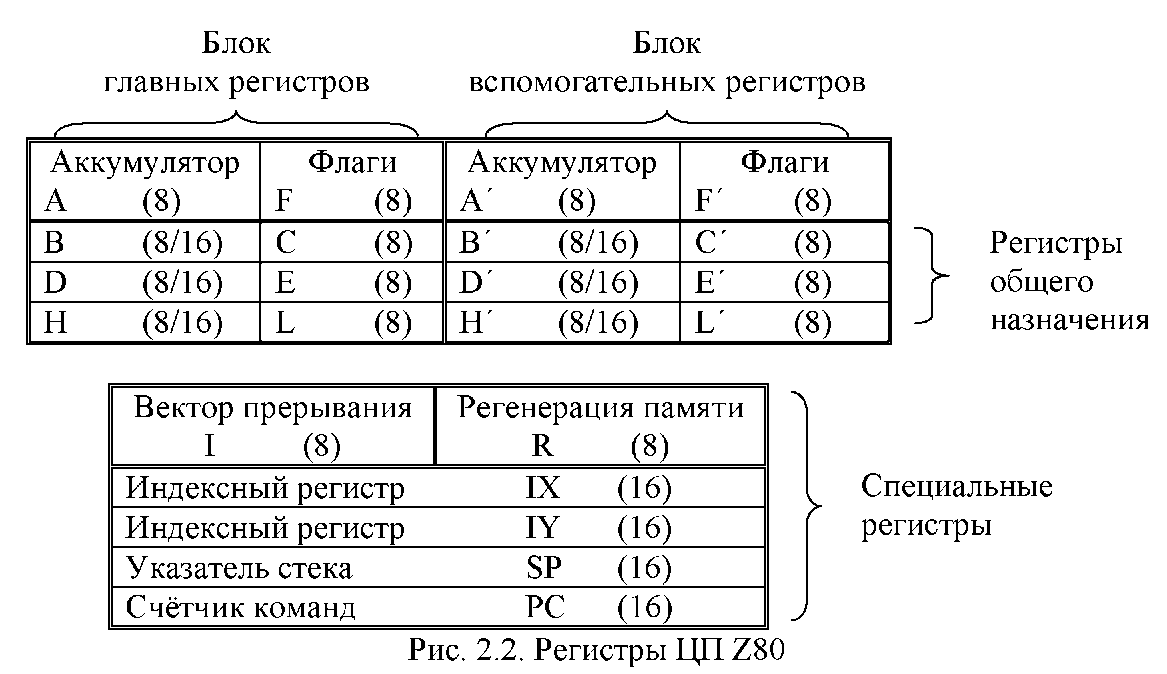

Программно доступными средствами ЦП являются 22 внутренних восьми- и

шестнадцатиразрядных регистра. Они образуют три блока: 2 альтернативных блока (главный и

вспомогательный) - по шесть 8-разрядных регистров, аккумулятору и регистру флагов в каждом, и

блок специальных регистров.

Специальные регистры

PC Program Counter - Счётчик команд

Счётчик команд является программно доступным регистром, и используемся для

приёма, преобразования и выдачи на шину адреса текущего 16-разрядного адреса команды.

Содержимое счётчика команд автоматически инкрементируется после выборки каждого

байта команды. В случаи перехода в программе, новый адрес автоматически заносится в

счетчик команд.

SP Btack Pointer - Указатель стека

Указатель содержит 16-разрядный адрес ячейки стека, к которой было последнее

обращение Содержимое SP декрементируется, когда данные загружаются в стек и

инкрементируется при чтении. Стек организуется во внешнем ОЗУ по принципу LIFO (Last

In - First Out). Обмен данными между стеком и ЦП может быть автоматическим (как в

случае обработки подпрограмм), либо командами PUSH и POP. Стек позволяет простую

реализацию многоуровневых прерываний, практически неограниченное вложение

подпрограмм и упрощение при многих видах обработки данных.

IX, IY Indexregisters - Индексные регистры

Каждый из этик двух регистров может содержать 16-разрядный базовый адрес,

используемый при индексной адресации. Базовый адрес складывается со смещением,

которое указано в команде в дополнительном коде. Их сумма образует действительный

адрес ячейки памяти, содержащей данные. Этот вид адресации удобен при обработке

таблиц и массивов.

I Interruptveotor register - Регистр вектора прерывания

Это 8-разрядный программно доступный регистр, используемый в режиме

прерывания 2 (IM2) Он содержит старший байт вектора прерывания. Младший байт

принимается от внешнего устройства. Путём их объединения формируется полный вектор

прерывание. (Подробнее см. гл. 6).

R Refreshregister - Регистр регенерации памяти

Это 8-разрядный программно доступный регистр, обеспечивавший возможность

использования динамических ОЗУ без внешних схем регенерации. Содержимое его

младших 7 разрядов автоматически увеличивается на единицу после каждой выборки

команды. При этом восьмой бит сохраняет значение, полученное при выполнении команды

загрузки этого регистра. Т.о. формируется адрес регенерации, который подается в младшую

часть адресной шины во время декодирования и выполнения команды в ЦП (в старшую

часть - содержимое регистра I). Регенерация данного вида называется "прозрачной" и не

снижает быстродействия процессора.

Главный и вспомогательный блоки регистров

ЦП Z80 содержит два альтернативных блока регистров: главный (A-L) и вспомогательный

(A'-L'). С точки зрения программиста оба блока абсолютно равноправны, но в данный момент

можно работать лишь с одним из них. Переключение этих блоков производится командами ЕХХ и

EX AF.AF'. Такая организация удобна тем, что позволяет быстро сохранить содержимое

регистровых блоков при вызове подпрограмм или при возникновении прерывания. Однако

следует помнить: отсутствует средство подтверждения, какой из блоков (главный или

вспомогательный) используется в данный момент.

A,A' Accumulator - Аккумулятор

Каждый из двух блоков регистров содержит по одному 8-разрядному аккумулятору.

При арифметических и логических операциях он служит источником одного из операндов

и, как правило, приёмником результата. Второй операнд берётся из другого регистра, либо

из памяти.

Диапазон представления целых чисел без знака в аккумуляторе от 0 до 255, со

знаком от -128 до +127.

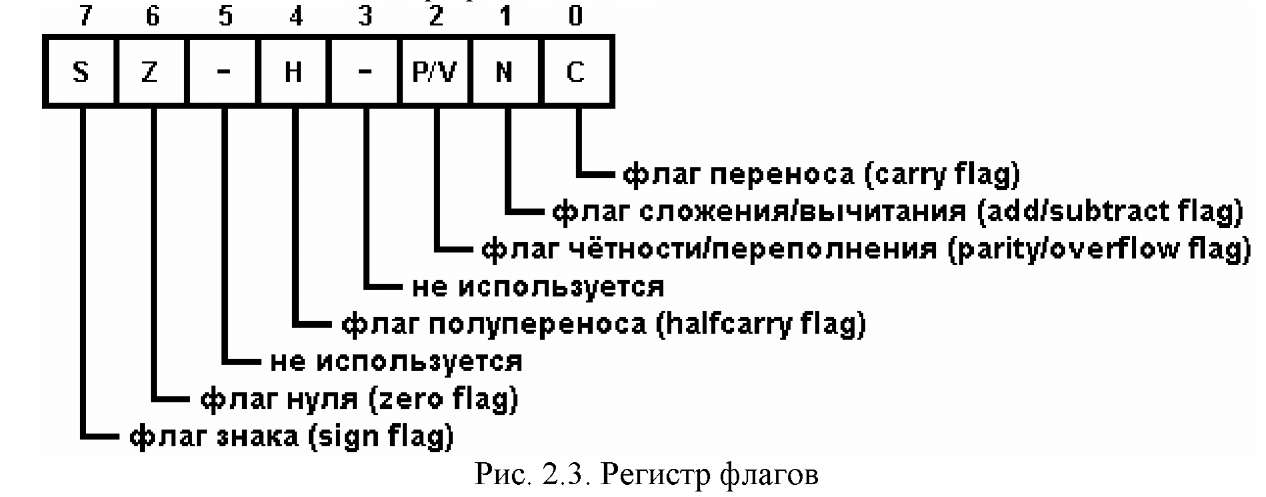

F,F' Flagregister - Флаговый регистр

В составе каждого блока регистров имеется свой флаговый регистр. Флаговый регистр

(называемый также регистром условий) содержит набор одноразрядных признаков, которые

устанавливаются по результату операции. Флаговые биты 7, 6, 2, 0 служат для реализации

условных переходов и условных вызовов подпрограмм или возвратов; биты 4 и 1 служат для

реализации двоично-десятичной арифметики.

Флаги устанавливаются в следующих условиях:

S=1, если результат операции отрицателен.

Z=1, если результат операции равен нулю.

Н=1, если при арифметической операции был перенос между битами 3 и 4.

P/V=1, а). если при логических операциях и командах сдвига количество установленных в

единицу битов чётно (функция четности P); б). если результат арифметической операции

находится вне диапазона представления чисел со знаком, т.е. меньше -128, либо больше +127

(функция переполнения V).

N=1, если в предыдущей команде выполнялось вычитание (команды типа SUB, DEC, CMP).

C=1, если при сложении возникает перенос из 7 бита аккумулятора, либо при вычитании -

заём. В командах сдвига состояние флага C однозначно соответствует сдвигаемому в него биту.

В, С, D, E, H, L Регистры общего назначения (РОН)

B', C', D', E', H', L'

Могут быть использованы как накопители данных или указатели адресов операндов. РОНы

могут использоваться как самостоятельные 8-разрядные регистры, либо как 16-разрядные

попарно: ВС, DE, HL и ВС', DE', HL'.

2.2. Ари^рме^ическо-логическое

ус^ройс^во (АЛУ)

В АЛУ выполняются арифметические и логические действия над 8-разрядными

операндами. Внутренне АЛУ связано с регистрами и через внутреннюю шину данных с внешней

шиной. В АЛУ выполняются следующие операции:

•S сложение;

•S вычитание

•S логическое И;

S логическое ИЛИ;

•S логическое исключающее ИЛИ;

•S сравнение;

•S увеличение на единицу;

•S уменьшение на единицу;

•S установка и сброс бита;

•S анализ значения бита;

•S сдвиг влево и вправо (арифметический и логический);

•S вращение влево и вправо (циклический сдвиг).

2.3. Регистр команд и ус^ройс^во

управление процессором

После извлечения команды из памяти, она загружается и регистр команд. Дешифратор

команд, входящий е устройство управления, преобразует код команды в управляющие сигналы:

•S внутренние, необходимые для считывания/записи данных в регистры и управления

АЛУ,

•S внешние, подаваемые на шину управления.

Кроме того, устройство управления реагирует на внешние управляющие сигналы.

2.4. Управление шиинами адреса и

данн^/х

Блок управления ША состоит из регистра адреса и буфера адреса. Буфер адреса

представляет собой выходные формирователи с тремя устойчивыми состояниями. Он

предназначен для выдачи 16-разрядного адреса из регистра адреса на шину.

Блок управления ШД представляет собой бинаправленную трёхстабильную схему,

применяемую для обмена информацией ЦП с внешними устройствами. При выводе информации

содержимое внутренней ШД запоминается в 8-разрядном регистре и через выходные

формирователи выдается на внешнюю вину данных.